# HfO<sub>2</sub>-based Metal-Oxide-Semiconductor Capacitors on n-InGaAs Substrate with a Thin Germanium Passivation Layer

Hyoung-Sub Kim<sup>a)</sup>, I. Ok, M. Zhang, F. Zhu, S. Park, J. Yum, S. Koveshnikov<sup>\*</sup>, W. Tsai<sup>\*</sup>, V. Tokranov<sup>\*\*</sup>, M. Yakimov<sup>\*\*</sup>, S. Oktyabrsky<sup>\*\*</sup>, and Jack C. Lee

\*Intel Corporation, Hillsboro, Oregon 97124, \*\*The University at Albany-SUNY, New York 12203, Dept. of Electrical Engineering, The University of Texas at Austin, Austin, Texas 78758

a) email: <a href="mailto:hskim1997@mail.utexas.edu">hskim1997@mail.utexas.edu</a>, phone: 512-471-1627

Keywords: InGaAs, GaAs, MOSCAP, HfO2, Passivation, Capacitance, Ge

# **Abstract**

The effect of a germanium (Ge) interfacial passivation layer (IPL) on the capacitance-voltage (C-V) and current density-voltage (J-V) characteristics of TaN/HfO2/Ge/nmetal-oxide-semiconductor capacitors (MOSCAPs) were studied. In comparison to MOSCAPs on GaAs, the results from the accumulation region were quite similar, while the C-V curves in the inversion region were substantially different owing to the different energy bandgap. By using 8 ~ 10 Å Ge IPL and 60~70 Å HfO2, MOSCAPs on InGaAs exhibited an equivalent oxide thickness (EOT) of ~ 11 Å and gate dielectric leakage current density ( $J_g$ ) of ~  $10^{-5}$  A/cm<sup>2</sup> at  $V_g$ - $V_{FB}$  =1 V with good C-V frequency dispersion, whereas poor electrical characteristics were obtained from the devices without a thin Ge IPL. These results show that a thin Ge IPL in optimal conditions passivates InGaAs surface effectively and provides a high quality interface.

# INTRODUCTION

One of the most challenging issues in III-V compound semiconductor devices is the lack of stable nature gate oxide like SiO<sub>2</sub> on Si substrate [1]. Recently, by employing silicon (Si) or germanium (Ge) interfacial passivation layers (IPL), remarkable results such as small capacitance-voltage (C-V) frequency dispersion, low Dit, and a thin equivalent oxide thickness (EOT) with low dielectric leakage currents have been achieved on GaAs substrate [2-3]. There has been very little work on InGaAs MOSCAPs with physical vapor deposition (PVD) Ge and HfO<sub>2</sub>, although a Ge IPL and HfO<sub>2</sub> dielectric have shown the possibility of effectively passivating GaAs surface to prevent it from Fermi level pinning and to provide excellent gate dielectric scalability from GaAs MOSCAPs. In this work, we present TaN/HfO<sub>2</sub> MOSCAPs on molecular beam epitaxy (MBE)-grown n-InGaAs layer using a thin Ge IPL.

### **DEVICE FABRICATION**

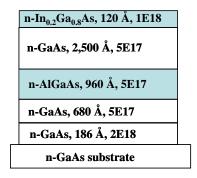

Figure 1 shows the schematic structure of an InGaAs layer epitaxially grown on a n-GaAs substrate. The doping

concentration of Si-doped  $In_{0.2}Ga_{0.8}As$  was  $1.0 \times 10^{18}/cm^3$ , which was higher than that of GaAs used in this work ( $2.0 \times 10^{17}/cm^3$ ). Ge/HfO<sub>2</sub>/TaN gate stacks were prepared by RF (Ge) and DC (HfO<sub>2</sub> and TaN) sputtering on the chemically cleaned (HCl + (NH<sub>4</sub>)<sub>2</sub>S) n-type GaAs and InGaAs samples. Post-deposition annealing (PDA) was performed at 600 °C in a N<sub>2</sub> (5% O<sub>2</sub>) ambient. A gate electrode was patterned using photolithography and reactive ion etching, and the Ohmic backside contact was formed using AuGe/Ni/Au.

Fig. 1. The schematic structure of an InGaAs layer

# RESULTS AND DISCUSSION

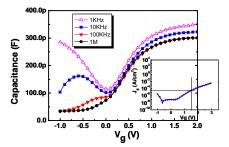

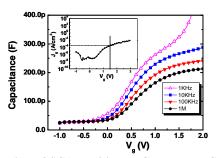

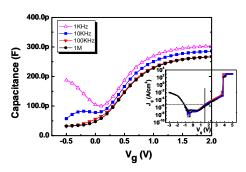

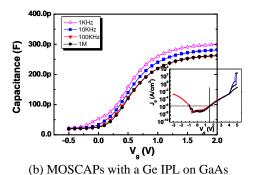

Figure 2 shows C-V curves with varying frequencies of the InGaAs MOSCAPs with (2a) and without (2b) a Ge IPL including the inset showing the J-V curves. In accumulation regime, higher capacitance (i.e. thinner EOT), smaller frequency dispersion and smaller J<sub>g</sub> were obtained from the device with a Ge IPL compared to those without an IPL as in GaAs MOSCAPs [3]. Figure 3 compares C-V and J-V curves of InGaAs (3a) and GaAs (3b) MOSCAPs with an optimum Ge IPL. Both devices went through the same fabrication processes such as a surface preparation, Ge IPL, HfO<sub>2</sub> (~75 Å), PDA, TaN for a fair comparison. In the accumulation region, almost similar results (EOT of ~ 13 Å,  $J_g$  of ~  $10^{-6}$  A/cm<sup>2</sup>) were obtained. The interface state densities (Dit) calculated using the conductance method for InGaAs and GaAs MOSCAPs were  $\sim 4.8 \times 10^{12}$  and  $\sim 3 \times 10^{12}$ 10<sup>12</sup> cm<sup>-2</sup>eV<sup>-1</sup>, respectively.

(a) MOSCAPs with a Ge IPL on InGaAs

(b) MOSCAPs without a Ge IPL on InGaAs

Fig. 2. C-V curves with varying frequencies ( $t_{HfO2} \sim 60\text{-}70\text{Å}$ ). The inset illustrates J-V curve.

(a) MOSCAPs with a Ge IPL on InGaAs

Fig. 3. C-V curves with varying frequencies ( $t_{HfO2} \sim 70-80\text{Å}$ ). The inset illustrates J-V curve

Table I summarizes electrical properties according to process conditions. Similar to GaAs MOSCAPs [4], the results from InGaAs MOSCAPs show that a too thin Ge IPL causes large frequency dispersion indicating a poor interface quality and that a too thick Ge IPL results in smaller capacitance, which indicates a poor interface quality and/or a contribution of Ge itself as a part of dielectrics. However, the devices with optimal Ge thickness (8-10 Å) and PDA condition (600 °C 40 s) show excellent C-V and J-V characteristics representing a high quality interface. In the inversion regions, C-V curves of the MOSCAPs with and without a Ge IPL on InGaAs are striking. It is worth mentioning that as Ge thickness increases and/or PDA time at a fixed temperature lengthens, the inversion capacitance becomes larger (see C<sub>inv.</sub>/C<sub>acc.</sub> ratios in table I). It can be explained that during process, Ga, As and/or In can outdiffuse leaving vacancies or antisite defects at the InGaAs side of the interface [5], which in turn act as recombinationgeneration centers, and the outdiffusion of As or Ga seems to be enhanced by a Ge layer because of the formation of an energetically favorable GeAs layer [5]. Those processinduced defects do not seem to significantly affect interface quality in the case of optimum conditions (optimal Ge thickness and PDA condition), considering the results from an optimum condition, but might deteriorate interface quality and junction leakage in metal-oxide-semiconductor field effect transistors as the Ge thickness increases and the PDA conditions become stronger. The high temperature (100 °C) measurement exhibited considerably increased inversion capacitance at the fixed frequencies indicating more minority carrier generation through these defects (Data are not shown here).

TABLE I C-V CHARACTERISTICS OF INGAAS MOSCAPS ACCORDING TO VARYING CONDITIONS

| GeIFL  | FDA        | Accumitation<br>Cap (pF) & HOT(Å)<br>@2 V & 1 MHz | Inversion Cap (pF)<br>@-0.5 V & 1 KF & | C <sub>in</sub> /C <sub>acc</sub><br>(%) | Fiequency<br>Dispersion<br>:%(%) | Frequency<br>Dispassion<br>: \( \Delta \text{V}_{\text{IB}}(\text{trik}) \) |

|--------|------------|---------------------------------------------------|----------------------------------------|------------------------------------------|----------------------------------|-----------------------------------------------------------------------------|

| ~0Å    | 500°C;300s | 165(23)                                           | 28                                     | 17                                       | 49.7                             | 390                                                                         |

|        | 600℃, 40s  | 213(17)                                           | 30                                     | 14                                       | 352                              | 260                                                                         |

|        | 600°C 180s | 249(14)                                           | 132                                    | 53                                       | 181                              | 150                                                                         |

| ~23Å   | 600°C, 10s | 295(11.4)                                         | 98                                     | 32                                       | 169                              | 120                                                                         |

|        | 600℃, 40s  | 293(11.5)                                         | 136                                    | 46                                       | 126                              | 80                                                                          |

|        | 600°C;300s | 273(124)                                          | 145                                    | 53                                       | 11.7                             | 40                                                                          |

| ~8·10Å | 600°C, 10s | 289(11.2)                                         | 181                                    | 66                                       | 91                               | 70                                                                          |

| Qtinum | 600℃, 40s  | 317(106)                                          | 216                                    | 68                                       | 7.6                              | 30                                                                          |

|        | 600°C;300s | 259(13.1)                                         | 197                                    | 76                                       | 10                               | 50                                                                          |

| ~3040  | 600°C, 10s | 209(17.6)                                         | 170                                    | 81                                       | 9.6                              | 200                                                                         |

|        | 600℃, 40s  | 170(234)                                          | 134                                    | 79                                       | 1                                | 40                                                                          |

|        | 600°C;300s | 132                                               | 116                                    | 88                                       | 61                               | -                                                                           |

#### **CONCLUSIONS**

Using a Ge IPL on a MBE-grown InGaAs layer, a high-quality interface between  $HfO_2$  and InGaAs surface has been implemented, leading to ultra-thin EOTs, excellent C-V frequency dispersion characteristics and low dielectric leakage current.

# ACKNOWLEDGEMENTS

This work was partially supported by Intel Corporation.

# REFERENCES

- [1] S. Tiwari et al., "Unpinned GaAs MOS Capacitors and Transistors," IEEE EDL, vol. 9, No. 9, pp. 488, 1988

- [2] I. Ok et al., "Self-Aligned n- and p-channel GaAs MOSFETs on Undoped and P-type Substrates Using HfO<sub>2</sub> and Silicon Interface Passivation Layer," IEEE IEDM 2006, pp. 829, 2006

- [3] H.-S. Kim et al., "Ultrathin HfO<sub>2</sub> (equivalent oxide thickness=1.1nm) metal-oxide-semiconductor capacitors on n-GaAs substrate with germanium passivation," Appl. Phys. Lett., 88, pp. 252906, 2006

- [4] H. S. Kim et al, "The effect of Germanium Interfacial Layer Thickness on Electrical Characteristics of HfO<sub>2</sub> MOSCAP on GaAs substrate," 2006 SISC Conf. Digest, p. 28, 2006

- [5] R. Bauer et al, "Surface process controlling MBE heterojunction formation: GaAs(100)/Ge interface," J. Vac. Sci. Technol., 21(2), p.491, 1982

# **ACRONYMS**

MOSCAP: Metal-Oxide-Semiconductor Capacitor

IPL: Interfacial Passivation Layer C-V: Capacitance-Voltage J-V: Current Density-Voltage PDA: Post-Deposition Annealing EOT: Equivalent Oxide Thickness PVD: Physical Vapor Deposition

MBE: Molecular Beam Epitaxy