## High Breakdown Voltage (1590 V) AlGaN/GaN-on-Si HFETs with Optimized Dual Field Plates

Jae-Gil Lee<sup>1</sup>, Bong-Ryeol Park<sup>1</sup>, Ho-Jung Lee<sup>1</sup>, Minseong Lee<sup>2</sup>, Hojung An<sup>2</sup> Kwang-Seok Seo<sup>2</sup> and Ho-Young Cha<sup>1\*</sup>

<sup>1</sup>School of Electronic and Electrical Engineering, Hongik University, Seoul 121-791, Korea <sup>2</sup>Department of Electrical Engineering and Computer Science, Seoul National University, Seoul 151-742, Korea \*hcha@hongik.ac.kr, +82-2-320-3062

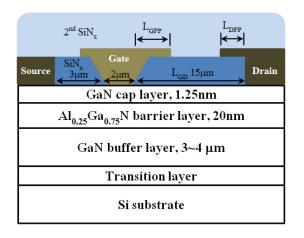

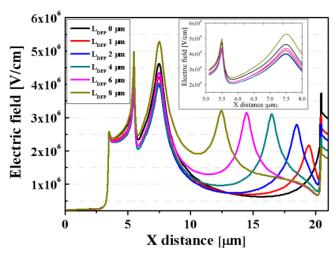

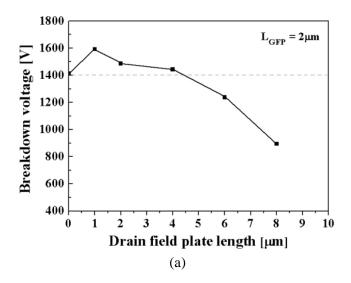

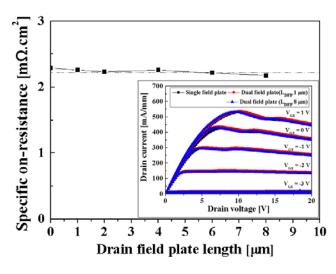

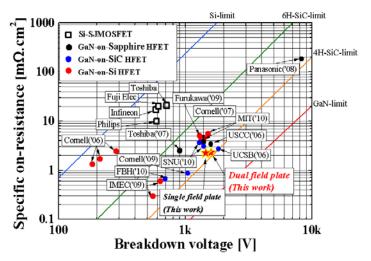

We have fabricated a state-of-the-art AlGaN/GaN-on-Si HFETs with dual field plates for high power conversion applications. Both gate and drain field plate lengths were varied for geometrical optimization. It was observed in our previous simulation study that a single gate field plate was enough to suppress the high electric field at the gate edge and in turn the device breakdown would rather be governed by the locally enhanced electric field at the drain side. In case the peak electric fields at the gate and field plate edges are lower than the critical electric field, the electric field at the drain side first reaches the critical level inducing the channel breakdown. Therefore, the breakdown voltage can be further improved by adding the drain field plate that spreads out the potential distribution near the drain side. In comparison with the optimized gate field plate structure, the breakdown voltage of the device fabricated using the optimized dual field plate structure was improved by 11.3%. A slight decrease in the on-resistance was observed for the dual field plate devices because of the positive bias on the drain field plate. It should be noted that no additional process is required to implement the dual field plate structure. The breakdown voltage of 1590 V with the on-resistance of 2.26 m $\Omega$ .cm<sup>2</sup> was achieved for the gate-to-drain distance of 15  $\mu$ m in which the gate and drain field plate lengths were 2 µm and 1 µm, respectively. Details about simulation analysis and device processing technology will be presented at the conference.

Fig 1. Cross-sectional view of AlGaN/GaN-on-Si HEMT with dual field plates.

Fig 2. Electric field distribution along the 2DEG channel at high drain bias for various drain field plate lengths. The gate field plate length was fixed to be  $2 \mu m$ .

Fig 3. (a) Measured breakdown voltage characteristics of the fabricated dual field plate devices as a function of drain field plate length. (b) Comparison of the breakdown characteristics between the optimized single gate field plate device and the optimized dual field plate device.

Fig 4. Specific on-resistance of the fabricated devices as a function of drain field plate length. The inset is the  $I_{\rm DS}$ - $V_{\rm DS}$  characteristics of the optimized dual field plate device.

Fig 5. Performance comparison with previously reported AlGaN/GaN devices.