## Effect of sputtered SiN passivation on current collapse of AlGaN/GaN HEMTs

Md. Tanvir Hasan<sup>1</sup>, Toshikazu Kojima, Hirokuni Tokuda, and Masaaki Kuzuhara<sup>2</sup>

Graduate School of Engineering, University of Fukui, 3-9-1 Bunkyo, Fukui 910-8507, Japan Email: \(^1\text{tan\_vir\_bd@yahoo.com}\), \(^2\text{kuzuhara@fuee.u-fukui.ac.jp}\), Phone: \(+81-776-27-9714\)

GaN-based HEMTs promise high power and high frequency operation due to the material advantages such as high breakdown field, high electron mobility, and high electron saturation velocity. Even though many progresses have been achieved, there still remains some issues especially dynamic on-resistance degradation or current collapse which seriously limits the microwave output power and switching performances. Although significant improvements have been achieved recently by various approaches such as surface passivation [1] and surface charge control with GaN cap layer [2], it is still a fundamental issue to understand the mechanism of the current collapse in detail. In this work, effects of sputtered SiN passivation on current collapse have been studied by monitoring the dynamic change in on-state resistance ( $R_{ON}$ ).  $R_{ON}$  ratio is also measured in terms of post-deposition annealing temperature.

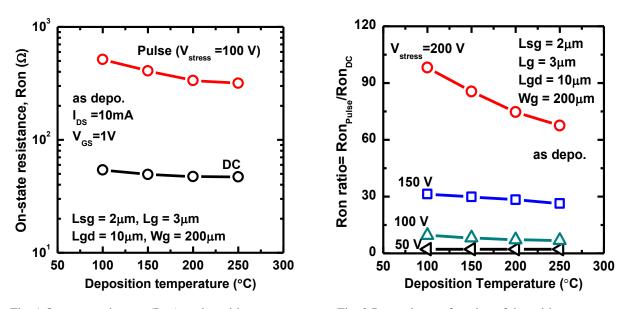

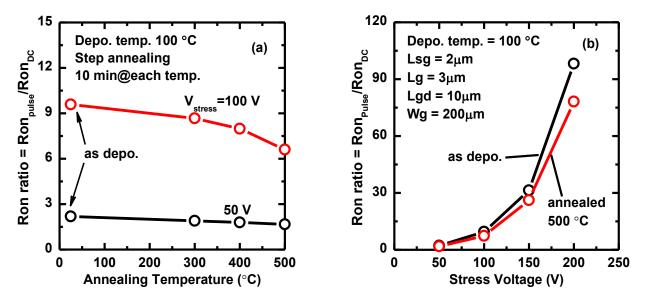

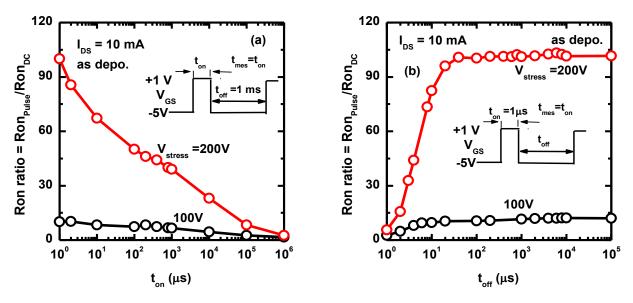

Figure 1 shows the deposition temperature dependency of  $R_{ON}$  for both  $R_{ON(DC)}$  and  $R_{ON(pulse)}$  (with  $V_{stress}$  =100V). The  $R_{ON}$  was decreased with increasing the deposition temperature. The amount of  $R_{ON}$  change was larger for pulsed measurement as compare to DC one. Figure 2 shows  $R_{ON}$  ratio as a function of deposition temperature with different  $V_{stress}$ . The  $R_{ON}$  ratio was also decreased with increasing the deposition temperature and became high with increasing  $V_{stress}$ . These results suggest that the SiN/AlGaN interface trap density is reduced with the increase in deposition temperature. Figure 3 shows the effect of post-annealing temperature on  $R_{ON}$  ratio with different  $V_{stress}$  for device A. The  $R_{ON}$  ratio was decreased with the increase in annealing temperature (see Fig. 3(a)). The consistent results were observed for higher  $V_{stress}$  (see Fig. 3(b)). These results also indicate that the SiN/AlGaN interface trap density is reduced with increasing the post-annealing temperature. Time dependent  $R_{ON}$  ratio was measured for device A, as shown in Fig. 4. The  $R_{ON}$  ratio was decreased with increasing  $t_{on}$  for a fixed  $t_{on}$  of  $t_{on}$  for a fixed  $t_{on}$  for a fi

<sup>[1]</sup> B. M. Green, et al., IEEE Electron Device Lett., vol. 21, pp. 268-270, June 2000

<sup>[2]</sup> T. Kikkawa, et al., in IEDM Tech. Dig., 2001, pp. 585-588.

Fig. 1 On-state resistance  $(R_{ON})$  vs deposition temperature. Fig. 2  $R_{ON}$  ratio as a function of deposition temperature.

Fig. 3  $R_{ON}$  ratio vs annealing temperature (a) and  $R_{ON}$  ratio vs stress voltage (b).

Fig. 4 Time dependent  $R_{ON}$  ratio for device A. On-state time (a) and off-state time (b).