# AlGaN/GaN MOS-HEMTs using RF Magnetron Sputtered SiO<sub>2</sub> Gate Insulator and Post-Annealing Treatment

Liang Pang, Ogyun Seok, and \*Kyekyoon (Kevin) Kim

Department of Electrical and Computer Engineering, University of Illinois at Urbana-Champaign, IL 61801 \*E-mail address: <a href="mailto:kevinkim@illinois.edu">kevinkim@illinois.edu</a>

Tel: (217)333-7162

# Keywords: GaN MOS-HEMT, Sputtered-SiO<sub>2</sub>, Post-annealing, Breakdown voltage

# Abstract

We propose high-quality RF magnetron sputtered SiO $_2$  gate insulator for high-voltage AlGaN/GaN MOS-HEMTs. A very high dielectric breakdown field over 9.6 MV/cm of SiO $_2$  insulator was achieved by adding oxygen flow during sputtering process. A post-annealing treatment was further developed to recover the sputtering-induced surface damage. After post-annealing, carrier concentration and mobility in 2DEG channel were improved by 21.7 and 5.5 %, respectively. As a result of optimized sputtering and post-annealing conditions, we achieved a very high breakdown voltage of 205 V at relatively short gate-drain distance of 2  $\mu$ m (breakdown field of 102.5 V/ $\mu$ m).

# INTRODUCTION

Although AlGaN/GaN HEMTs have attracted considerable attention for high-power, high-speed, and high-temperature applications, a relatively large leakage current through Schottky-gate contact and the surface traps remain as a serious problem [1]. In order to improve reverse blocking characteristics, significant progress has been made on MOS-HEMTs using various insulating materials.

A SiO<sub>2</sub>/AlGaN/GaN MOS-HEMT is a suitable structure for suppression of leakage current and increase of breakdown voltage due to the wide bandgap of SiO<sub>2</sub> and the high conduction band offset at SiO<sub>2</sub>/GaN interface [2]. However, further investigation into SiO<sub>2</sub> gate insulator is required to increase breakdown voltage and V<sub>GS</sub> sweeping range. Various deposition techniques, such as PECVD, Ebeam evaporation, and ALD, have been reported for deposition of SiO<sub>2</sub> on GaN devices [3-5].

In this paper, we propose RF magnetron sputtered  $SiO_2$  and optimize its deposition and post-treatment conditions for high-voltage AlGaN/GaN MOS-HEMTs. RF magnetron sputtering has proved to be capable of depositing  $SiO_2$  on GaN with quality better than the above-mentioned techniques [6], the reason being that energetic particle impingement can make the growing film more condense thus enhancing the oxide breakdown field. However, due

to the difficulty in preventing the bombardment damage to the GaN epilayer that degrades the 2DEG properties, there are very few reports on the successful fabrication of AlGaN/GaN MOS-HEMTs employing sputtered SiO<sub>2</sub> gate insulator.

# OPTIMIZATION OF SiO<sub>2</sub>-SPUTTERING CONDITIONS

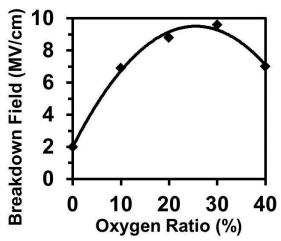

$Al/SiO_2/n^+$ -GaN (n = 1.4 × 10<sup>19</sup> cm<sup>-3</sup>) MOScapacitors were fabricated to examine breakdown field of the SiO<sub>2</sub> film under different deposition conditions. The sputtering was carried out at room temperature with a constant power of 160 W. Argon/oxygen gas mixtures were used as the sputtering gas with the ratio from 0 to 40 % to find optimum condition for high breakdown field. The breakdown voltage of the SiO<sub>2</sub> film strongly depends on oxygen flow rate as shown in Fig. 1. The breakdown voltage was improved with increase of oxygen ratio up to 30 % to achieve the highest value of 9.6 MV/cm. The oxygen flow introduces oxygen atoms into the film and densifies SiO2 insulator. Beyond 30 % oxygen ratio, breakdown voltage started to decrease, which is attributed to the reduction of energy input into the film due to the smaller atomic mass of O than Ar, reducing the film density. The sheet carrier concentration and the electron mobility in SiO<sub>2</sub>/AlGaN/GaN sample using 30 % oxygen condition were decreased by 25 and 69 % due to sputtering damage to AlGaN surface. These damages were recovered after post-annealing treatment as shown in Table 1. It is seen that the postannealing at 900 °C for 20 s is able to fully restore the epilayer crystallinity and interface quality. The largest breakdown field of 9.6 MV/cm is higher than that of the SiO<sub>2</sub> films deposited on GaN by any other techniques including PECVD, photo-CVD, and Ebeam evaporation [7-9].

Fig. 1: Breakdown field of the sputtered-SiO2 films on  $n^+$ -GaN as a function of oxygen ratio in the sputtering gas.

Table 1: Values of the electron concentration  $(n_s)$  and mobility  $(\mu)$  under different annealing temperatures and durations.

| Experimental conditions | Electron mobility (cm²/V·S) | Sheet concentration<br>(×10 <sup>13</sup> cm <sup>-2</sup> ) |

|-------------------------|-----------------------------|--------------------------------------------------------------|

| Epilayer                | 1060                        | 1.08                                                         |

| RTA (0 °C, 0 s)         | 330                         | 0.81                                                         |

| RTA (800 °C, 20 s)      | 644                         | 0.98                                                         |

| RTA (900 °C, 20 s)      | 1118                        | 1.32                                                         |

| RTA (1000 °C, 20 s)     | 1077                        | 1.30                                                         |

| RTA (900 °C, 10 s)      | 941                         | 0.99                                                         |

| RTA (900 °C, 30 s)      | 1116                        | 1.31                                                         |

| RTA (900 °C, 60 s)      | 974                         | 1.25                                                         |

# ALGAN/GaN MOS-HEMTS USING RF-SPUTTERED SiO<sub>2</sub> GATE INSULATOR

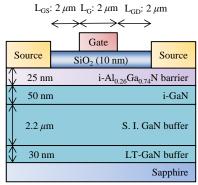

of Cross-sectional view the fabricated SiO<sub>2</sub>/AlGaN/GaN MOS-HEMT is shown in Fig. 2. 220 nm-deep mesa isolation and 40 nm-deep recessed source/drain etching were carried out by using Cl<sub>2</sub>based ICP-RIE. Next, 10-nm SiO<sub>2</sub> was sputtered at room temperature with O<sub>2</sub>/Ar ratio of 30 %, which is the optimized condition, and showed the highest dielectric breakdown field. Ti/Al/Ti/Au were then deposited by E-beam evaporation as the Ohmic contacts, followed by post-annealing in N<sub>2</sub> ambience. Deposition of gate metals (Ni/Au) completed the fabrication process. As for the device dimensions, the gate length, width, source-to-drain, and gate-to-drain distances were 2, 100, 6, and 2  $\mu$ m, respectively.

Table 1 shows the values of  $n_s$  and  $\mu$  under different annealing temperatures or durations. It is seen that the post-annealing at 900 °C for 20 s is able to fully recover the sputtering-induced surface damage to epilayer. The additional improvement in both  $n_s$  (21.7%) and  $\mu$  (5.5%) is due to the chemical

passivation of the exposed epilayer surface dangling bonds by the SiO<sub>2</sub> film. Further increase in the annealing temperature or time resulted in reduction of  $n_s$  and  $\mu$  again, owing to the defect generation by AlGaN/GaN film dissociation at the elevated temperature, which degraded the epilayer crystallinity and channel interface morphology. Furthermore, it was found that the optimized postannealing condition coincides with that of the GaNbased Ohmic metal annealing for Ti/Al contact scheme, which is generally performed at 850~900 °C for 20~30 s. Therefore, the two annealing steps can be combined into one to save the thermal cost and simplify the fabrication process. As a result, our process may be considered to have the lowest thermal energy requirement to realize MOS-HEMTs among all the dielectric deposition techniques, which is certainly beneficial for commercial applications.

Fig. 2: Cross-sectional view of the fabricated  $SiO_2/AlGaN/GaN$  MOS-HEMT.

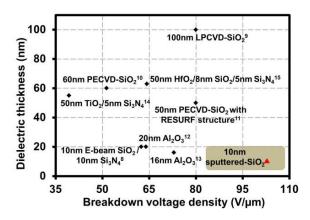

Output I-V and transfer curve of SiO<sub>2</sub>/AlGaN/GaN MOS-HEMT using the optimized annealing temperature of 900 °C are shown in Fig. 3. For the characterization, the gate leakage current of the MOS-HEMT was first compared with that of the conventional HEMT of the same dimensions. It was found that at a reversed gate bias of -30 V, more than four orders of magnitude lower leakage current was achieved by using the MOS-HEMT. The peak drain current and the maximum transconductance were 594 mA/mm and 74.5 mS/mm, respectively. The threeterminal off-state breakdown voltage was measured by a curve tracer and was 205 V. A comprehensive comparison of the breakdown voltages per unit gatedrain distance, obtained from various publications [8-15], is presented in Fig. 4. The dielectric thickness is also taken into consideration since a direct comparison using MOS-HEMTs with the same dielectric thickness is difficult. The breakdown voltage performance of our device is, if not better, at least on-par with other GaN-based MOS-HEMTs reported to date.

Fig. 3: (a) Output *I-V* and (b) transfer characteristics of the SiO<sub>2</sub>/AlGaN/GaN MOS-HEMT with 10-nm-thick sputtered-SiO<sub>2</sub>.

Fig. 4: Comparison of breakdown voltage density of MOS-HEMTs achieved by different groups.

# **CONCLUSIONS**

Using room-temperature RF magnetron sputtering with a 30% oxygen mixing, highly condensed  $SiO_2$  has been demonstrated to be a suitable gate insulator for AlGaN/GaN MOS-HEMTs. In addition, post-

annealing treatment during Ohmic contact formation removed the sputtering-induced damage to GaN epilayer, resulting in a MOS-HEMT with high saturation current and off-state breakdown voltage.

#### ACKNOWLEDGEMENTS

Support provided in part by the Strategic Research Initiatives Program of the College of Engineering at the University of Illinois at Urbana-Champaign. The MOCVD AlGaN/GaN templates used in this work were provided by Kyungpook National University, Korea for which we are grateful to Prof. Jung-Hee Lee and Mr. Dong-Seok Kim.

### REFERENCES

- [1] I. Daumiller, et al., IEEE Electron Device Lett. 20, 448 (1999).

- [2] M. A. Khan, et al., Appl. Phys. Lett. 77, 1339 (2000).

- [3] S. Arulkumaran, et al., J. J. Appl. Phys. 44, L812 (2005).

- [4] Z. H. Liu, et al., IEEE Electron Device Lett. 31, 803 (2010).

- [5] L. Pang, et al., J. Phys. D, Appl. Phys. 45, 045105 (2012).

- [6] H. Ueda, et al., J. J. Appl. Phys. 48, 126001-1 (2009).

- [7] Y. Z. Chiou, et al., IEEE T. Electron Device 50, 1748 (2003).

- [8] N. Q. Zhang, Ph.D dissertation, Univ. CA, Santa Barbara, 2002.

- [9] K. Matocha, et al., IEEE T. Electron Device 52, 6 (2005).

- [10]H. Kambayashi, *et al.*, Solid-State Electron. **54**, 660 (2010).

- [11]Y. Niiyama, et al., Furukawa Rev. **36**, 1 (2009).

- [12]M. Kanamura, et al., IEEE Electron Device Lett. 31,189(2010).

- [13] P. D. Ye, et al., Appl. Phys. Lett.86, 063501 (2005).

- [14] S. Yagi, et al., J. J. Appl. Phys. 46, 2309 (2007).

- [15] S. Yagi, et al., Phys. Status Solidi c 4, 2682 (2007).

# **ACRONYMS**

HEMT: high electron mobility transistor

MOS: metal-oxide-semiconductor

2DEG: 2-dimensional electron gas

PECVD: plasma-enhanced chemical vapor deposition

ALD: atomic layer deposition

n<sub>s</sub>: electron concentration

$\mu$ : electron mobility

RTA: rapid thermal annealing