# Highly Linear Ka-Band 0.15µm GaAs Power pHEMT Process for Use in Low-Cost Molded QFN Plastic Package

Michael Hosch<sup>1\*</sup>, Hermann Stieglauer<sup>1</sup>, Charles Teyssandier<sup>2</sup>, Philippe Auxemery<sup>2</sup>, Mikael Richard<sup>2</sup>, Jan Grünenpütt<sup>1</sup>, Benoît Lambert<sup>2</sup>, Didier Floriot<sup>2</sup>, and Hervé Blanck<sup>1</sup>

<sup>1</sup>United Monolithic Semiconductors GmbH, Wilhelm-Runge-Straße 11, 89081 Ulm, Germany <sup>2</sup>United Monolithic Semiconductors SAS, 10 Avenue du Québec, 91140 Villebon-sur-Yvette, France \*e-mail: michael.hosch@ums-ulm.de, phone: +49-731-505-3085

Keywords: GaAs, Power pHEMT, Linearity, Plastic Package

#### **Abstract**

Next generation communication radio systems are designed to use highly linear but low-cost power amplifiers in the Ka-band. To serve this demand, United Monolithic Semiconductors has developed a 0.15µm GaAs power pHEMT process offering outstanding transistor level linearity while maintaining state-of-theart RF power density and gain performance up to 40GHz. This technology called PPH15X-20 can be used in low-cost molded QFN plastic packages without any RF performance degradation. In this paper, we want to present the key figures of merit of this technology including two-tone on-wafer linearity performance.

## INTRODUCTION

Today's market already offers power amplifier products in the Ka-band with good linearity and gain performance serving the demand for next generation communication radio systems [1,2]. However, these products have a major disadvantage related to the need for humidity robustness, while maintaining good RF performance. Therefore, these products need to be put in very expensive hermetic air cavity packages. This is necessary since the RF performance of the chip would be significantly degraded when adding a final chip protection layer. Such a chip protection layer is needed to protect the chip against humidity and for compatibility with cheap non-hermetic molded QFN plastic packages. To satisfy all of the requirements of a low-cost molded QFN plastic package, including good linearity, gain performance and robustness against humidity, UMS has developed a second generation of its 0.15µm Ka-band GaAs power pHEMT technology, called PPH15X-20.

#### TECHNOLOGY DESCRIPTION

The PPH15X-20 technology utilizes a classical pseudomorphic AlGaAs/InGaAs/GaAs double recess HEMT structure. The 0.15 $\mu$ m T-gate is formed by a dielectric assisted gate process. It is designed for an operation voltage of  $V_{\rm DD}=6V$ . The typical electrical DC and RF device characteristics are summarized in table I.

$TABLE\ I$  Typical DC and RF Device Parameters of PPH15X-20

| DC Parameters (1x100µm Device) |                    |            |       |

|--------------------------------|--------------------|------------|-------|

| Parameter Name                 | _                  | Values     | Units |

| Maximum Drain Current          | $I_{DS+}$          | 570        | mA/mm |

| Drain Saturation Current       | $I_{DSS}$          | 350        | mA/mm |

| Maximum Transconductance       | $G_{max}$          | 480        | mS/mm |

| Threshold Voltage              | $V_{g,100}$        | -0.95      | V     |

| Three-Terminal Breakdown       | $V_{BDS}$          | ≥12        | V     |

| Gate-Drain Diode Breakdown     | $V_{\mathrm{BGD}}$ | ≥-13       | V     |

| Small-Signal RF Paran          | neters (2x75µ      | ım Device) |       |

| Parameter Name                 |                    | Values     | Units |

| Input Capacitance              | $C_{in}$           | 130        | fF    |

| Feedback Capacitance           | $C_{\mathrm{f}}$   | 15         | fF    |

| Output Resistance              | R <sub>out</sub>   | 400        | Ω     |

| Extrinsic RF Transconductance  | Gme                | 60         | mS    |

In comparison to the first generation technology called PPH15X-10 [3], the gate module has been modified. A big part of the SiN used for device passivation has been replaced by a low dielectric material around the gate. This modification leads to a significantly reduced feedback capacitance C<sub>f</sub>, reducing the influence of higher level SiN layers on the small-signal capacitances and supports the robustness of the device against humidity. Besides these positive effects, this kind of gate passivation eliminates the negative impact of the final chip protection on the intrinsic capacitances of the device which typically causes a degradation of the overall RF performance of the device. Additionally, the process offers two interconnect metal layers, where one can be optionally re-enforced for higher current density capability, as well as two thin film resistor layers with  $30\Omega_{\square}$  and  $1000\Omega_{\square}$ , respectively. Furthermore, two capacitor densities with 260pF/mm<sup>2</sup> and 625pF/mm<sup>2</sup> can be integrated. When chips are put into non-hermetic plastic or air-cavity packages, a final chip protection is offered. The backside process is a 70µm process with individual-throughwafer-source-vias.

#### RF DEVICE CHARACTERIZATION

## Small-Signal Characterization:

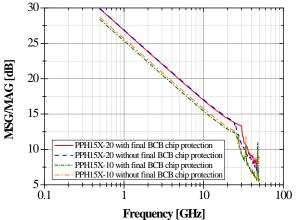

To characterize the gain improvement achieved mainly by the reduction of the small-signal feedback capacitance, as described in the section before, wafers with and without final BCB protection have been characterized by Sparameter measurements up to 50GHz. The maximum gain MSG/MAG has been calculated from these S-parameters and plotted versus frequency in Fig. 1.

Fig. 1: MSG/MAG determined by S-parameter measurement up to 50GHz performed on a  $8x75\mu m$  device at  $V_{DS}=6V$ .

As can be seen, the small-signal RF gain is not impacted by the BCB protection. Whereas the first generation technology clearly shows a RF gain drop by approx. 0.5 dB when the final BCB chip protection is applied. The graph also shows the clear gain improvement by 1.5 dB as compared to the first generation technology due to the reduction of the feedback capacitance  $C_f$ .

## Large-Signal Characterization:

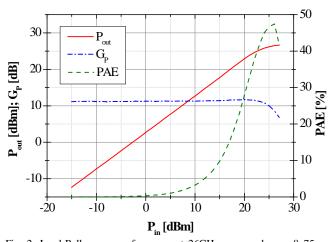

Fig. 2: Load-Pull power performance at 26GHz measured on a 8x75  $\mu m$  device at  $V_{DS} = 6V.$

To assess the large-signal RF characteristics of the technology, on-wafer single-tone load-pull measurements have been carried out. These measurements have been performed on a representative  $8x75\mu m$  device in  $\mu\text{-strip}$  configuration at the desired operation voltage of  $V_{DS}=6V$ . The on-wafer single-tone load-pull measurements performed at 26GHz depicted in fig. 2 give a power density at the 1-dB-compression point of  $P_{\text{-}1dB}=750mW/mm$ . The linear power gain is  $G_p=11dB$  and the peak Power Added Efficiency is  $\eta_{PAE}=48\%$ .

## Two-Tone Linearity Characterization:

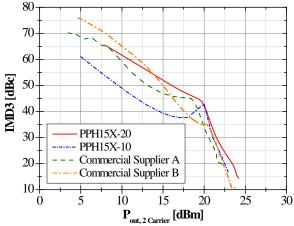

The on-wafer two-tone load-pull measurements have been performed at 10GHz with a tone spacing of 10MHz. To determine the two-tone linearity performance represented by the third-order intermodulation distance IMD3, the IMD3 is plotted versus the respective two-tone output power. The results are compared to the first generation technology as well as to two commercial technologies. The results are depicted in Fig. 3.

Fig. 3: Two-tone linearity performance versus output power at 10GHz and a tone spacing of 10MHz measured on a  $8x75\mu m$  device at  $V_{DS}=6V$ .

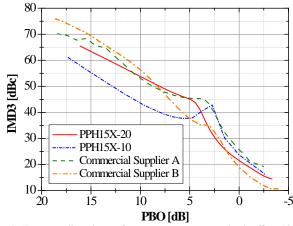

Fig. 4: Two-tone linearity performance versus power back-off at 10GHz and a tone spacing of 10MHz measured on a  $8x75\mu m$  device at  $V_{DS}=6V$ .

It can bee seen that PPH15X-20 is presenting a very linear IMD3 performance up to the output power compression level without any sweet-spot formation. Especially in the range of 6...8dB PBO towards P<sub>-1dB</sub> the technology is even showing slightly better linearity performance than all three compared technologies, as can be seen in Fig.4 where the IMD3 is plotted versus PBO. This area is of special interest for the design of highly linear PAs for communication applications since the designs are optimized in this PBO region to achieve good linearity at a reasonably high output power level.

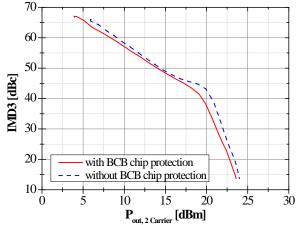

To investigate the impact of the final BCB chip protection layer on the linearity performance, devices with and without final BCB protection have been characterized by two-tone load-pull measurements and compared. The two-tone linearity results shown in Fig. 5 prove that the final BCB chip protection does not degrade the linearity perfomance either. The small difference observed here is well within the the measurement accuracy of a two-tone load-pull system.

Fig. 5: Two-tone linearity performance at 10GHz and a tone spacing of 10MHz measured on a  $8x75\mu m$  device at  $V_{DS}=6V$ .

This investigation highlights the fact that the intrisic RF performance of the device is not impacted at all by applying a final BCB chip protection. To this end, it can be stated, that the performance in a QFN package is also unchanged when the chip is overmolded.

## RELIABILITY ASSESSMENT

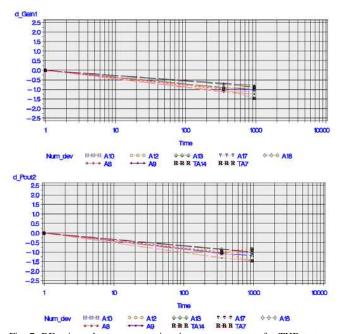

Long-term accelerated life tests on single-stage  $50\Omega$ -matched amplifiers called DECs have been carried out to assess the reliability of the process. An example of RF gain and output power interim measurements during a HTOL test at a junction temperature of  $270^{\circ}\text{C}$  is plotted in Fig. 6.

The output power degradation during HTOL tests is the limiting factor. The MTF of this test is  $T_{50\%} = 1980h$  for a failure criterion of 1dB output power degradation. Based on preliminary life-tests at different junction temperatures a life time of more than 40 years has been extracted.

Fig. 6: RF gain and output power interim measurements of a HTOL test at a junction temperature of 270°C for 2000h.

To assess the robustness against humidity, full MMICs have been tested in an open package in biased temperature humidity tests (THB). The test conditions are a case temperature of  $T_C = 85^{\circ}C$  and a relative humidity of 85% while the devices are biased at  $V_{DS} = 6V$  with a power consumption of P < 200 mW (according to JEDEC JESD22-A101C) [4].

Fig. 7: RF gain and output power interim measurements of a THB test on full MMIC chips using a final BCB chip protection for 1000h.

Fig. 7 shows the interim measurements of RF gain and output power. Over the test duration of 1000h no catastrophic failures have been observed. This test demonstrates the high robustness of the process against humidity. Therefore, it can be used in non-hermetic packages like molded QFN without any humidity issues.

CONCLUSIONS

A second generation 0.15µm Ka-band GaAs power pHEMT technology has been presented. The technology is developed for the design of highly linear power amplifiers for communication systems up to 40GHz. The RF power and linearity characterization has demonstrated desirable stateof-the-art performance competitive with the technologies on the market. It has been shown that the process has improved RF performance and is compatible with a final BCB chip protection without any negative impacts. Furthermore, humidity tests have demonstrated a high intrinsic robustness of the process against humidity. Finally, it has been proven that UMS' PPH15X-20 process is highly compatible with low-cost molded QFN packages without any performance degradation, while maintaining robustness against humidity in these non-hermetic packages. To the best of our knowledge, this is the first technology available on the world-wide market offering outstanding RF performance up to 40GHz in low-cost molded QFN plastic packages.

## ACKNOWLEDGEMENTS

The authors would like to thank MC<sup>2</sup> at University of Lille for close collaboration with on-wafer single-tone and two-tone load-pull characterization.

## REFERENCES

- [1] C. F. Campell, et al., *High Efficiency Ka-Band Power Amplifier MMIC Utilizing a High Voltage Dual Field Plate GaAs PHEMT Process*, Compound Semiconductor Integrated Circuit Symposium (CSICS), Waikoloa, HI, USA, October 2011.

- [2] M. Chertouk, et al., Manufacturable 0.15 um PHEMT Process for High Volume and Low Cost on 6" GaAs Substrates: The First 0.15 μm PHEMT 6"GaAs Foundry Fab, Technical Paper, WIN Semiconductors, http://www.winsemiconductorscorp.com/

- [3] J. Grünenpütt, et al., UMS GaAs Process Developments for Space, Workshop, 7<sup>th</sup> European Microwave Integrated Circuits Conference, Amsterdam, The Netherlands, October 2012.

- [4] JEDEC, Steady State Temperature Humidity Bias Life Test, JEDEC JESD22-A101C, March 2009, http://www.jedec.org/

#### **ACRONYMS**

**HEMT: High Electron Mobility Transistor**

BCB: Benzocyclobutene PAE: Power-Added-Efficiency

IMD3: Third-Order Intermodulation Distance

PBO: Power Back-Off PA: Power Amplifier

**DEC: Dynamic Evaluation Circuit**

HTOL: High-Temperature Operation Life-Test

THB: Temperature-Humidity-Biased-Test