# Thin Al<sub>0.5</sub>Ga<sub>0.5</sub>N/GaN HEMTs on QuanFINE® Structure

Ding-Yuan Chen<sup>1, 2</sup>, Kai-Hsin Wen<sup>1, 2</sup>, Mattias Thorsell<sup>2</sup>, Olof Kordina<sup>1</sup>, Jr-Tai Chen<sup>1</sup>, and Niklas Rorsman<sup>2</sup>

dychen@swegan.se, +46-702033691

<sup>1</sup>SweGaN AB, Olaus Magnus väg 48A, 583 30, Linköping, Sweden.

<sup>2</sup>Chalmers University of Technology, Kemivägen 9, 412 58, Göteborg, Sweden.

Keywords: RF, AlGaN, GaN, HEMTs, QuanFINE®, and Short channel effect.

# **Abstract**

The performance of HEMTs fabricated on a thin Al<sub>0.5</sub>Ga<sub>0.5</sub>N/GaN heterostructure with a total barrier thickness of 6.5 nm is presented and benchmarked to the epi-structure with a 13 nm thick Al<sub>0.3</sub>Ga<sub>0.7</sub>N barrier on an identical QuanFINE® structure. DC characteristics on both samples with a gate length of 100 nm demonstrate a high current above 1 A/mm. A higher extrinsic g<sub>m</sub> of 550 mS/mm is measured on the sample with a thinner high Al content barrier. Moreover, low trapping effects with a 12-14 % buffer-related dispersion at a  $V_{DSQ}$ of 25 V are characterized for both samples, which indicate of the iron-free **QuanFINE®** advantage heterostructure.

### INTRODUCTION

GaN HEMTs are gaining attention in the applications of high-frequency devices due to high breakdown voltage and high electron mobility, which yield a high power density with good efficiency. AlGaN barrier with a thickness above 10 nm and the Al composition beneath 30 % is commonly utilized for GaN HEMTs [1]. However, the transconductance (g<sub>m</sub>) is limited due to the thick barrier layer. Therefore, a thinner AlGaN barrier with higher Al content (>30 %) is proposed to improve gate response [2]. Lattice-matched InAlN barrier is another approach to reduce the barrier thickness, which has a higher 2DEG density than the AlGaN barrier thanks to a stronger polarization force. However, plausible Indium aggregation in the barrier might limit the reliability of devices [3].

The buffer is conventionally Fe or C doped to render good isolation [4]. However, devices made on Fe- or C-doped buffers suffer from trapping effects. Recently, a novel QuanFINE® heterostructure, which has a thin UID-GaN layer sandwiched in between a barrier and an AlN nucleation layer, potentially allows the AlN nucleation layer to act as a backbarrier and to reduce the trapping effects [5, 6].

In this study, the first demonstration of a high Alcontaining thin Al<sub>0.5</sub>Ga<sub>0.5</sub>N barrier on a QuanFINE® structure was investigated. Device fabrication with DC and pulsed-IV characterization will be presented.

## **EPI-GROWTH**

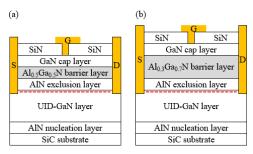

The epitaxial layers were grown on a semi-insulating SiC substrate utilizing a MOCVD by SweGaN. Using SweGaN proprietary epitaxial growth process, a low thermalboundary-resistance AlN nucleation layer was grown and followed with a 250 nm UID-GaN layer [5, 6]. On top of this, a 5.0 nm Al<sub>0.5</sub>Ga<sub>0.5</sub>N layer (1.5 nm AlN exclusion layer and 3.5 nm Al<sub>0.5</sub>Ga<sub>0.5</sub>N layer), and a 1.5 nm GaN cap layer were grown as the active layers (denoted as Al<sub>50</sub>, Fig. 1a). A n<sub>s</sub> of  $1.22 \cdot 10^{13} \, \text{cm}^{-2}$  and a  $\mu_e$  of 1700 cm<sup>2</sup>/V s were characterized by contactless Hall measurements (Lehighton) and R<sub>sh</sub> of 315  $\Omega$ /sq was characterized by Eddy current measurement after epitaxial growth. These values demonstrate the good 2DEG properties achievable with a thin Al<sub>0.5</sub>Ga<sub>0.5</sub>N barrier on QuanFINE®-structure. The other epi-structure which has an 1 nm AlN exclusion layer, a 10 nm Al<sub>0.3</sub>Ga<sub>0.7</sub>N barrier layer, and a 2 nm GaN cap layer with a n<sub>s</sub> of 1.16·10<sup>13</sup> cm<sup>-2</sup>, μ<sub>e</sub> of 2030 cm<sup>2</sup>/V·s, and R<sub>sh</sub> of 286 Ω/sq was grown on nominal QuanFINE®-structure (denoted as Al<sub>30</sub>, Fig. 1b) to benchmark to Al<sub>50</sub>. [6]

# DEVICE FABRICATION

The epi-wafers were cleaned by the RCA cleaning process followed by a passivation-first 60 nm thick SiN layer deposited by LPCVD before device processing. Mesa etching was defined for device isolation and the ohmic contacts were achieved by deeply recessed Ta-based metal stacks [7]. A low  $R_{\rm c}$  of ~0.3  $\Omega mm$  for both samples is characterized by TLM measurements. Two-fingers gates with passivation-assisted field plates, which have an  $L_{\rm g}$  of 100 nm and a gate width of  $2x50~\mu m$  were defined by e-beam lithography with metal evaporation followed by lift-off process (Fig. 1).

Fig. 1. Schematic of device layout for (a) Al<sub>50</sub> and (b) Al<sub>30</sub>.

#### **HEMTs Results**

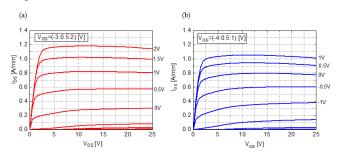

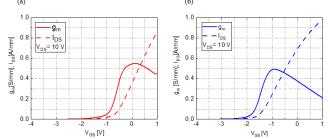

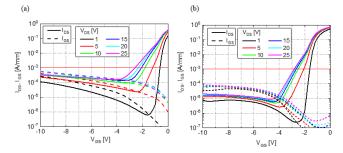

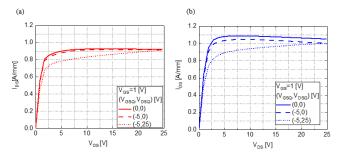

Different I-V measurement windows (V<sub>GS</sub>) were performed on two samples due to the shifting of V<sub>TH</sub>. HEMTs on both samples show a high I<sub>DS</sub> of ~1.1 A/mm (Fig. 2). A higher extrinsic  $g_m$  of 550 mS/mm and a  $V_{TH}$  of -0.9 V were measured on  $Al_{50}$  as compared to that on  $Al_{30}$  with a  $g_m$  of 500mS/mm and a V<sub>TH</sub> of -1.8 V (Fig. 3) [6], which are mainly caused by a thinner AlGaN barrier. Short channel effects are revealed on Al<sub>50</sub> and Al<sub>30</sub> at high drain bias with an average DIBL shifting of 82 mV/V, and 50 mV/V, respectively, extracted at the I<sub>DS</sub> of 1 mA/mm, while over the range of measured V<sub>DS</sub> from 1 to 25 V (Fig. 4). A higher leakage current was measured on Al<sub>50</sub>, which might be caused by a thinner barrier with a different Schottky barrier condition. These results indicate that further buffer confinement and mitigation of leakage currents are required for short gate length devices.

Fig. 2. I-V measurements for (a) Al<sub>50</sub> and (b) Al<sub>30</sub>.

Fig. 3. g<sub>m</sub> measurements for (a) Al<sub>50</sub> and (b) Al<sub>30</sub>.

Fig. 4. DIBL measurements for (a) Al<sub>50</sub> and (b) Al<sub>30</sub>.

A low surface-related current collapse of 0.5% and 4% were measured on  $Al_{50}$  and  $Al_{30}$ , respectively, which indicate that the LPCVD SiN passivation is compatible with different barrier design (Fig. 5). Moreover, low buffer-related dispersion of 12% and 14% for  $Al_{50}$  and  $Al_{30}$ , respectively,

highlight the advantage of using QuanFINE®, which removes the intentional iron and carbon dopants in GaN.

Fig. 5. Pulsed-IV measurements for (a) Al<sub>50</sub> and (b) Al<sub>30</sub>.

# **CONCLUSIONS**

A 50% Al content thin AlGaN barrier is successfully grown on QuanFINE® heterostructure with excellent 2DEG properties. High  $I_{DS\text{-sat}}$  and  $g_m$  combined with low trapping effects can potentially translate to a better large-signal RF performance. Further improvements of the 2DEG confinement from the backside such as inserted AlGaN backbarrier and/or reduced UID-GaN layer thickness of QuanFINE® are required for highly down-scaled HEMT technologies.

# ACKNOWLEDGMENTS

This work was performed in part in the Competence Center for III-Nitride Technology C3Nit-Janzén with financial support from the VINNOVA via grant no. 2016-05190, and in part in the project "Ultra-Compact AESA Technology for Autonomous Aircrafts" with financial support from the VINNOVA via grant no, 2017-04870, and in part in the project "CoolHEMT" with financial support from the European Union's Horizon 2020 research and innovation program via grant no, 823260. The HEMT fabrication was performed in the Nanofabrication Laboratory at Chalmers, part of Myfab.

# REFERENCES

- [1] J. Bergsten *et al.*, "AlGaN/GaN high electron mobility transistors with intentionally doped GaN buffer using propane as carbon precursor," *Japanese Journal of Applied Physics*, vol. 55, no. 5S, p. 05FK02, 2016.

- [2] T. Zimmermann *et al.*, "AlN/GaN insulated-gate HEMTs with 2.3 A/mm output current and 480 mS/mm transconductance," *IEEE Electron Device Letters*, vol. 29, no. 7, pp. 661-664, 2008.

- [3] A. Malmros *et al.*, "Impact of channel thickness on the large-signal performance in InAlGaN/AlN/GaN HEMTs with an AlGaN back barrier," *IEEE Transactions on Electron Devices*, vol. 66, no. 1, pp. 364-371, 2018.

- [4] J. Bergsten *et al.*, "Electron trapping in extended defects in microwave AlGaN/GaN HEMTs with carbon-doped buffers," *IEEE Transactions on*

- Electron Devices, vol. 65, no. 6, pp. 2446-2453, 2018.

- [5] J.-T. Chen *et al.*, "A GaN–SiC hybrid material for high-frequency and power electronics," *Applied Physics Letters*, vol. 113, no. 4, p. 041605, 2018.

- [6] D.-Y. Chen *et al.*, "Microwave Performance of 'Buffer-Free' GaN-on-SiC High Electron Mobility Transistors," *IEEE Electron Device Letters*, vol. 41, no. 6, pp. 828-831, 2020.

- [7] Y.-K. Lin *et al.*, "A versatile low-resistance ohmic contact process with ohmic recess and low-temperature annealing for GaN HEMTs," *Semiconductor Science and Technology*, vol. 33, no. 9, p. 095019, 2018.

## **ACRONYMS**

HEMTs: High electron mobility transistors

Lg: Gate length

I<sub>DS</sub>: Drain-source current

I<sub>DS-sat</sub>: Drain-source saturation current

R<sub>c</sub>: Contact resistance R<sub>sh</sub>: Sheet resistance n<sub>s</sub>: 2DEG concentration μ<sub>c</sub>: Electron mobility

2DEG: Two dimensional electron gas UID-GaN: Unintentional doped-GaN

LPCVD: Low pressure chemical vapor deposition

V<sub>GS</sub>: Gate-source voltage V<sub>TH</sub>: Threshold voltage

DIBL: Drain induced barrier lowering