# Nanocrystalline Diamond-Capped β-(Al<sub>x</sub>Ga<sub>1-x</sub>)<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> Heterostructure Field-Effect Transistor

Hannah N. Masten<sup>1\*</sup>, James Spencer Lundh<sup>1</sup>, Joseph A. Spencer<sup>2,3</sup> Tatyana Feygelson<sup>2</sup>, Jennifer Hite<sup>2</sup>, Daniel Pennachio<sup>2</sup>, Alan G. Jacobs<sup>2</sup>, Boris Feygelson<sup>2</sup>, Kohei Sasaki<sup>4</sup>, Akito Kuramata<sup>4</sup>, Pai-Ying Liao<sup>5</sup>, Peide Ye<sup>5</sup>, Bradford Pate<sup>2</sup>, Karl D. Hobart<sup>2</sup>, Travis J. Anderson<sup>2</sup>, Marko J. Tadjer<sup>2</sup>

<sup>1</sup>National Research Council Postdoctoral Fellow at U.S. Naval Research Laboratory,

<sup>2</sup>U.S. Naval Research Laboratory, Washington, DC, USA, <sup>3</sup>Virginia Tech, Blacksburg, VA, USA, <sup>4</sup>Novel Crystal Technology, Inc., Japan <sup>5</sup>Purdue University, West Lafayette IN, USA.

\* Email: Hannah.masten.ctr@nrl.navy.mil, phone : (980)-297-8556

# Keywords: Gallium Oxide, Nanocrystalline Diamond, Thermal management, Heterojunction field-effect transistor

#### ABSTRACT

In this work, we detail our fabrication process for incorporating a nanocrystalline diamond heat-spreading layer onto a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> transistor as a candidate solution for top-side device-level thermal management for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices. The resulting nanocrystalline diamond (NCD) capped  $\beta$ -(Al<sub>x</sub>Ga<sub>1-x</sub>)<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> heterostructure field-effect transistors show maximum DC power densities of  $\geq$  6.4 W/mm and a 40% decrease in the thermal resistance at the gate.

# INTRODUCTION

The ultra-wide bandgap semiconductor, β-Gallium Oxide ( $\beta$ -Ga<sub>2</sub>O<sub>3</sub>), shows tremendous promise for next-generation power devices due to its high expected critical field strength of 6-8 MV/cm and the availability of high-quality single crystalline bulk substrates [1]. The low thermal conductivity (highest of 0.27 W (cm K)<sup>-1</sup> in [010] direction), though, is a well-known challenge for devices based on this semiconductor [1,2]. The development of high-performance β-Ga<sub>2</sub>O<sub>3</sub>-based power devices will require the incorporation of thermal management solutions [2]. Nanocrystalline diamond (NCD) can be used as an effective heat spreading layer for device-level thermal management [2] and has previously been incorporated into AlGaN/GaN devices [3,4]. Here, we demonstrate an NCD-capped  $\beta$ -(Al<sub>x</sub>Ga<sub>1-x</sub>)<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> heterostructure field-effect transistor (HFET) as a potential solution for top-side device-level thermal management for Ga<sub>2</sub>O<sub>3</sub> power devices.

#### FABRICATION PROCESS

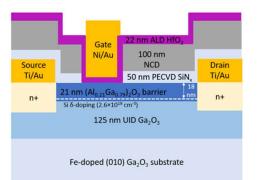

Figure 1 shows a cross-section schematic of the fabricated NCD-capped  $\beta$ -(Al<sub>x</sub>Ga<sub>1-x</sub>)<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> HFET. First,  $\beta$ -(Al<sub>x</sub>Ga<sub>1-x</sub>)<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> heterostructures were grown via ozone-assisted molecular beam epitaxy (O<sub>3</sub>-MBE) and consisted of a 125 nm thick unintentionally doped (UID) Ga<sub>2</sub>O<sub>3</sub> layer followed by a 28 nm thick (Al<sub>0.19</sub>Ga<sub>0.81</sub>)<sub>2</sub>O<sub>3</sub> (AlGaO) barrier layer on an Fedoped (010) Ga<sub>2</sub>O<sub>3</sub> substrate [5]. The AlGaO layer was deltadoped with Si ~3 nm above the interface. Both the AlGaO and

Fig. 1. Cross-section schematic of the  $\beta$ -(Al<sub>x</sub>Ga<sub>1-x</sub>)<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> HFET with NCD heat-spreading layer.

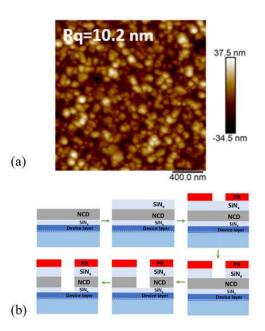

Fig. 2. (a) AFM of the NCD layer grown on the AlGaO/Ga<sub>2</sub>O<sub>3</sub> heterostructure. Roughness was approximately 10.2 nm. (b) Process (clockwise) for removal of the SiN<sub>x</sub>/NCD stack within the gate region.

the Ga<sub>2</sub>O<sub>3</sub> layers were continuously grown in the MBE reactor, preventing unintentional Si from accumulating at the interface. Si ion implantation (activation anneal: 30 min, 925 °C in N<sub>2</sub>) and e-beam evaporation of Ti/Au (anneal: 1 min, 470 °C in N<sub>2</sub>) was used to form Ohmic source/drain contacts. The specific contact resistivity, mobility, sheet carrier concentration, and sheet resistance at room temperature were measured to be  $4.3 \times 10^{-4} \ \Omega \times cm^2$ , 54 cm<sup>2</sup>/V·s,  $1.26 \times 10^{13} \ cm^{-2}$ , and 9.1 k $\Omega/\Box$ , respectively.

The next step in the fabrication process was to grow the NCD layer on the AlGaO/Ga<sub>2</sub>O<sub>3</sub> heterostructure. The NCD layer is grown by microwave plasma enhanced CVD (MW-CVD), which requires the use of Hydrogen plasma. Hydrogen plasma has been shown to severely damage  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> and its alloys by etching deep pits into the surface. Because of this and also to provide a suitable surface for nanodiamond seed dispersion, a protective SiN<sub>x</sub> barrier dielectric was deposited prior to NCD CVD. In this work, a  $\sim 50 \text{ nm SiN}_x$  layer was deposited by plasma-enhanced chemical vapor deposition (PECVD) at 400°C before the NCD growth process started. NCD nucleation sites were facilitated via a seeding method using detonation nanodiamond powder. The growth chamber was pre-treated with 200 sccm of H<sub>2</sub> at a temperature of 100 °C and a pressure of 15 torr for 1 h. NCD growth was then performed using a 1.5% CH<sub>4</sub>/H<sub>2</sub> concentration at a temperature of 400 °C, pressure of 15 torr, and power of 800 W for ~6 h. The resulting NCD film thickness was ~100 nm

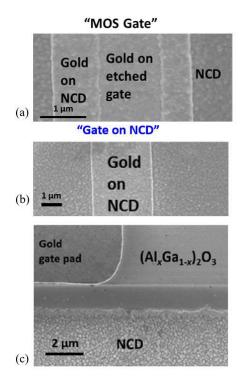

Fig. 3. SEM images of the gate for (a) the "MOS gate" and (b) the "Gate on NCD", and (c) an image showing the full removal of the  $SiN_x/NCD/SiN_x$  stack. Grains observed in the region labeled "gold on etched gate" in (a) is most likely from the evaporated gold, similar to the grains observed in (c) in the gold gate pad.

and fig. 2 (a) shows an atomic force microscopy (AFM) image of the surface.

In order to finish the NCD-capped AlGaO/Ga<sub>2</sub>O<sub>3</sub> HFET, the SiN<sub>x</sub>/NCD stack must be removed from the gate region and the source/drain probing pads. An additional SiN<sub>x</sub> layer was deposited by PECVD on top of the NCD film to act as a hard mask for the plasma etching process. After standard lithography, SF<sub>6</sub> (ICP 200 W, RF 50 W) was used to etch the top SiN<sub>x</sub> mask. O<sub>2</sub> plasma with ICP 1000 W and RF 100 W was used to etch the NCD layer, followed by a second SF<sub>6</sub> etch to remove the SiN<sub>x</sub> interlayer. This process is illustrated in Fig. 2 (b).

Lastly, a 22nm  $HfO_2$  gate dielectric was deposited by atomic layer deposition, and the gate contacts were formed by lift-off of a 20/200 nm thick Ni/Au metal stack. The resulting device cross-section schematic is shown in Fig. 1. Figure 3 shows secondary electron microscopy (SEM) images of the gate regions of two of the devices, (a) and (b), that will be discuss in the results and (c) a region where the NCD film was fully removed. Thermal measurements were performed using a TMX Scientific T°Imager (532 nm, 100X objective); power dissipated was monitored using an oscilloscope, and the base temperature was maintained at 20 °C.

# RESULTS AND DISCUSSION

Two types of devices were investigated in this work. Figure 3 (a) shows an image of the gate for the first device, referred to as "MOS gate"; here, the  $SiN_x/NCD/SiN_x$  stack was fully etched from the gate region. Figure 4 (a) and (b) show the DC transfer and output characteristic for the "MOS gate" NCD-capped AlGaO HFET. A low on-state  $I_D$  (max of 6.8 mA/mm) was observed, which may be caused by SF<sub>6</sub>-plasma damage to the AlGaO channel when removing the NCD/SiN<sub>x</sub> film

Fig. 1. DC transfer characteristics (a) and (c) and output characteristics (b) and (d) of

$\beta$ -(Al<sub>x</sub>Ga<sub>1-x</sub>)<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> HFETs with the MOS gate (a, b) and with the gate on top of NCD (c, d). The devices both have the following geometry: L<sub>GS</sub> = 2.5 µm, L<sub>GD</sub> = 10 µm, and W<sub>G</sub> = 75 µm.

from the gate region. The other device, called "Gate on NCD", is shown in fig. 3 (b) where the gate region was not fully etched before gate metal deposition. DC transfer and output measurements are shown in Fig. 4 (c) and (d) for this device which is still capped with NCD within the gate region. On-state I<sub>D</sub> was over 10X higher when the AlGaO barrier in the gate region was not exposed to the  $O_2$  plasma and  $SF_6$ etches required to remove the NCD and SiN<sub>x</sub> layers, respectively. While the SiN<sub>x</sub>/NCD stack did protect the AlGaO active region from plasma damage, the large negative threshold voltage of the "Gate on NCD" device shows why the stack removal in the gate region is necessary. The process for removing the SiN<sub>x</sub> interlayer will need to be optimize to achieve excellent device characteristics with the incorporation of this thermal management technique.

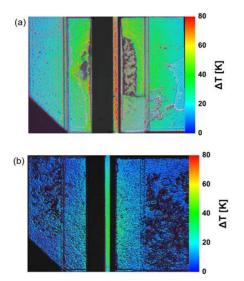

A maximum power density of ~6.4 W/mm, with a gate voltage of 0 V, was measured before catastrophic failure occurred on the "Gate on NCD" device. Figure 5 shows thermoreflectance images of (a) a reference uncapped device and (b) the "Gate on NCD" HFET. The power density of both devices is ~ 1.5 W/mm. The device without NCD showed a temperature rise at the gate of ~73 K, while the NCD-capped device only saw an increase of ~35 K. These images show that the NCD heat-spreading layer has great potential as a thermal management technique for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices.

# CONCLUSION

Self-heating in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices due to the material's low thermal conductivity is a significant issue that must be mitigated in the development of these power devices. Here, we demonstrated a  $\beta$ -(Al<sub>x</sub>Ga<sub>1-x</sub>)<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> heterostructure field-effect transistor with a nanocrystalline diamond heatspreading capping layer. The NCD film was able to significantly reduce the temperature rise observed at the gate at a given power density. A maximum power density of 6.4 W/mm was reached with the NCD-capped device. Plasma damage from the removal of the SiN<sub>x</sub>/NCD stack within the gate region was shown to have a negative impact on the device characteristics. Optimization of the SiN<sub>x</sub>/NCD etch within the gate region will be required to maintain good device performance. Further improvements to the NCD layer (thicker NCD films, higher growth temperatures, etc.) will lead to this being an excellent thermal management technique for Ga<sub>2</sub>O<sub>3</sub>-based power devices.

Fig. 5. Thermoreflectance images of a reference uncapped device (a) and the "Gate on NCD" HFET (b), both at a power density of  $\sim$ 1.5 W/mm.

#### ACKNOWLEDGEMENT

J.S.L. and H.N.M. gratefully acknowledge support by the NRC postdoctoral fellowship program. Research at the NRL was supported by the ONR. Research at NCT, Inc. was partially supported by ONR Global.

#### REFERENCES

- Masataka Higashiwaki, *et al.*, Semicond. Sci. Technol. 31 034001 (2016).

- [2] Mohamadali Malakoutian, et al., Appl. Phys. Express 14 055502 (2021).

- [3] Marko Tadjer, et al., Phys. Status Solidi A, 213 893-897 (2016).

- [4] T. J. Anderson, *et al.*, ECS J. Solid State Sci. Technol., 6 Q3036 (2017).

- [5] M.J. Tadjer, et al., J. Vac. Sci. Technol. A 39, 033402 (2021).

#### ACRONYMS

AlGaO:  $\beta$ -(Al<sub>x</sub>Ga<sub>1-x</sub>)<sub>2</sub>O<sub>3</sub>

HFET: Heterostructure field-effect transistor

MW-CVD: microwave plasma enhanced chemical vapor deposition

NCD: Nanocrystalline diamond