# AlN/GaN/InGaN Coupling Channel HEMTs with Improved SS Performance

Hao Lu<sup>1\*</sup>, Xiaohua Ma<sup>1</sup>, Bin Hou<sup>1</sup>, Ling Yang<sup>1</sup>, and Yue Hao<sup>1</sup>

<sup>1</sup>School of Microelectronics, Xidian University, Xi'an, 710071, China. E-mail stress: luhao@stu.xidian.edu.cn. Phone number: +86 187-9270-3042

# Keywords: Aluminium nitride; Gallium nitride; HEMT; Subthreshold swing; Channel engineering

#### **Abstract**

The realization of wide bandgap material in CMOS digital applications will bring great advantages of high temperature and high reliability. In this work, we have reported the AIN/GaN/InGaN coupled-channel HEMT with improved subthreshold characteristics. The subthreshold swing below the ideality value of 60 mV/dec at room temperature has been achieved. To study the physical mechanism of the steep SS, we carried out the temperature-dependent IV measurements. The hot carrier transfer mechanism is responsible for these excellent device performances. The hot carrier transfer mechanism was modulated by the different transverse channel electric field, proved by  $V_{DS}$ - and  $L_{g}$ - dependent transfer I-V characteristics. This work is believed to encourage further study of the AlN/GaN/InGaN platform to power the future III-Nitrides CMOS technology.

## Introduction

GaN HEMTs have been widely reported for high-frequency RF and high voltage power switch applications due to their excellent material properties [1], [2]. However, the GaN devices need to be utilized with a Si-based CMOS peripheral logic circuit for the real application, which will bring additional parasitic and chip areas. In view of this, the researchers are continuing to develop the application of wide bandgap material platforms of group III-Nitrides as CMOS digital circuits.

To push the realization of group III-nitrides in CMOS applications will possess great advantages of high temperature and high reliability. Recent significant progress in GaN/AlN p-channel transistors has facilitated GaN CMOS technology developing rapidly for digital applications [3], [4]. The subthreshold slope (SS) is of vital importance for high-speed switching in low power and low voltage logic applications. Si/Ge CMOS and III-V platform has been extensively researched for digital applications. Hence, the steep SS performance of GaN n-FET is meeting great requirements. However, the existing reports of steep subthreshold properties are based on AlGaN or InAlN systems [5]-[7]. To the authors' best knowledge, there are no reports on the steep subthreshold properties of AlN systems, which can co-integrate with the GaN/AlN p-channel platform.

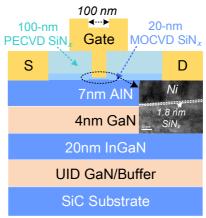

Fig. 1. Cross sectional schematic device structure of the AlN/GaN/InGaN CC-HEMTs. The inset is the HRTEM image of the  $SiN_x$  under the gate.

In this work, we reported an AlN/GaN/InGaN coupling-channel HEMT (CC-HEMT) where enhanced steep subthreshold characteristics. The fabricated transistors exhibit excellent characteristics, including steep subthreshold swing (SS) of 39 mV/dec was observed. The transverse-dependent hot carrier transfer mechanism is responsible for this excellent device performance. The results presented here are believed to boost the AlN system as a viable integration platform for future III-Nitrides high-speed switching digital applications.

## DEVICE STRUCTURE AND FABRICATION

The AlN/GaN/InGaN CC-HEMT, with the structure schematic shown in Fig. 1, were grown on a 3-inch semi-insulating 4H-SiC substrate by MOCVD, as consistent with our early work [8]. The epitaxial layers comprise an AlN nucleation layer, a doped GaN buffer layer, unintentionally doped (UID) GaN layer, 20 nm InGaN channel layer, 4 nm GaN channel, 7 nm AlN barrier layer, and 20 nm *in situ* SiN passivation layer from down to top.

The device processing started with the ohmic contact formation. Prior to the ohmic metal being deposited, the *in situ*  $SiN_x$  layer was removed in the source/drain pad area to form direct ohmic contact to AlN barrier. A Ti/Al/Ni/Au

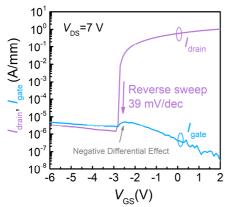

Fig. 2. Transfer I-V characteristics of AlN/GaN/InGaN HEMTs in semi-log scale under reverse sweep of  $V_{\rm GS}$ .

(20/160/55/45 nm) metal stack was deposited by electronbeam evaporation. 2DEG isolation was performed by N+ ion implantation. And to suppress the surface trapping effect, the transistor was deposited with 100 nm PECVD  $SiN_x$ . When it comes to the gate processing, the gate foot was opened using  $CF_4$ -based plasma etching to remove  $SiN_x$ , leaving *in situ*  $SiN_x$  at a depth of 1.8 nm to alleviate the gate leakage current as shown in HRTEM (the inset in Fig. 1), followed by Ni/Au Schottky contact for the gates was deposited. The gate length of the reported device is 100 nm defined by electron-beam lithography.

# RESULTS AND DISCUSSION

The transfer I-V characteristics were measured at  $V_{\rm ds}$ =7 V under the reverse sweep of  $V_{\rm GS}$  (Fig. 2). The SS were observed for below the ideality of 60 mV/dec at room temperature. To further investigate this, we need to analyze the theoretical formulation of SS. According to the SS expression [9]:

$$SS = \frac{\partial V_{gs}}{\partial (\log_{10} I_d)} = \frac{\partial V_{gs}}{\partial \Psi_s} \cdot \frac{\partial \Psi_s}{\partial (\log_{10} I_d)} = mkT/q \times \ln(10),$$

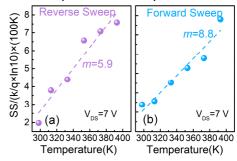

where m is the body factor:  $m=1+C_s/C_{ins}$ , determining the value of SS. The SS of sub-60 mV/dec means the observation of numerical negative capacitance effect for the AlN/GaN/InGaN CC-HEMT. In order to investigate the physical mechanism of the steep SS, the temperature-dependent I-V measurement was performed.

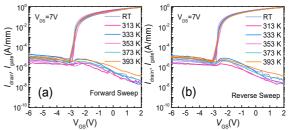

Fig. 3 shows the temperature-dependent I-V curve of the AlN/GaN/InGaN CC-HEMTs ranging from RT to 393 K under the forward/reverse sweep of  $V_{\rm GS}$ . As shown in Fig. 4, the body factor m extracted from the SS as a function of temperature showed both > 1, which indicated that the sub-60 mV/dec is not caused by the negative capacitance effect. Hence, the AlN/GaN/InGaN CC-HEMT is not negative capacitance field effect transistor (NCFET), we should consider another physical mechanism. The gate current shows a negative differential resistance with  $V_{\rm GS}$  variation, which is similar to [6]. Therefore, the hot carrier transfer between the

Fig. 3. Transfer I-V characteristics of the AlN/GaN/InGaN CC-HEMTs under the (a) forward and (b) reverse sweep of  $V_{\rm GS}$  with temperature variation.

Fig. 4. The measured and fitted SS versus temperature of AlN/GaN/InGaN CC-HEMTs under the forward/reverse sweep of  $V_{\rm GS}$ .

channel and gate reported can explain the acquisition of the sub-60 mV/dec SS [6]. It should be noted that the SS under the forward sweep of  $V_{\rm GS}$  is also below 60 mV/dec, indicating that the coupling effect between the channel to channel also participates in the low SS value in this regime, which will be discussed in detail in future work. It is due to the hot electron transfer that the actual effect of gate voltage is enhanced in the process of forward and reverse sweep of  $V_{\rm GS}$ , then the ON/OFF of the device is accelerated. Hence, the SS achieves an ultra-low value due to the above mechanism.

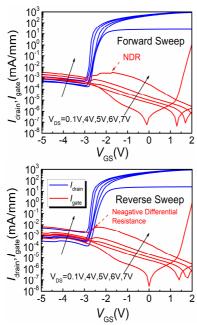

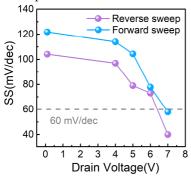

To verify the hypothesis of hot carrier transfer, the transfer I-V characteristics under the forward/reverse sweep with  $V_{\rm ds}$  variation were measured using Agilent B1500 semiconductor parameter analyzer after considering the hot electron transfer is extremely dependent on channel transverse electric field. As shown in Fig. 5, the drain current curve in the subthreshold region show drastic change with the drain voltage increased, while the negative differential effect (NDR) of the gate current curve also appeared at the same time. The extracted SS (Fig. 6) demonstrated that the SS decreases with the increase of drain voltage, especially achieved sub-60 mV/dec of SS at  $V_{\rm DS} = 7$  V.

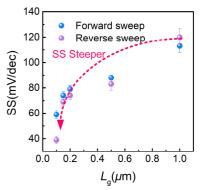

The gate length is also an important factor affecting the channel transverse electric field. When the gate length is shorter, especially below the sub-micron length, the channel transverse electric field is stronger. Fig. 7 illustrates the SS characteristics of the AlN/GaN/InGaN CC-HEMT with  $L_{\rm g}$  variation under the forward/reverse sweep of  $V_{\rm GS}$ . It can be seen that the SS drastically decreases with the gate dimension

Fig. 5. Transfer I-V characteristics of the AlN/GaN/InGaN CC-HEMTs under the (a) forward and (b) reverse sweep of  $V_{\rm GS}$  with  $V_{\rm GS}$  variation.

Fig. 6. The extracted SS of the AlN/GaN/InGaN CC-HEMTs under the (a) forward and (b) reverse sweep of  $V_{\rm GS}$  with  $V_{\rm DS}$  variation.

scaling down, which indicates that the hot carrier transfer occurs with the change of the transverse electric field under the gate.

#### CONCLUSIONS

In this work, we have reported the AlN/GaN/InGaN CC-HEMT with a superior subthreshold swing of sub-60 mV/dec characteristics. The hot carrier transfer mechanism proved by the  $V_{\rm DS}$ - and  $L_{\rm g}$ - dependent transfer I-V characteristics, is responsible for these excellent device performances. This work is believed to encourage further study of the AlN/GaN/InGaN platform to power the future III-Nitrides CMOS technology.

Fig. 7. The extracted SS of the AlN/GaN/InGaN CC-HEMTs under the forward and reverse sweep of  $V_{\rm GS}$  with  $L_{\rm g}$  variation.

### ACKNOWLEDGEMENTS

The authors would like to thank Zeyan Si and Teng Huo for their help with the on-wafer temperature-variation IV test. The authors would also like to appreciate the full personnel of the national engineering research center of wide band-gap semiconductor for the high quality and fast wafer processing.

This work was supported by the National Natural Science Foundation of China under Grants 62104184, 62090014, and 62188102, in part by the Fundamental Research Funds for the Central Universities of China under Grants XJS201102, XJS211101, XJS211106, and ZDRC2002.

## REFERENCES

[1] U. K. Mishra, et al., Proc. IEEE 96, 287-305 (2008).

[2] Y. Hao, et al., IEEE Electron Device Lett. **32**, 626-628 (2011).

[3] K. Nomoto, et al., 2020 IEEE International Electron Devices Meeting, pp. 8.3.1-8.3.4, Dec 2020.

[4] S. J. Bader, et al., 2019 IEEE International Electron Devices Meeting, pp. 4.5.1-4.5.4, Dec 2019.

[5] H. W. Then, et al., 2013 IEEE International Electron Devices Meeting, pp. 28.3.1-28.3.4, Dec 2013.

[6] P. Cui, et al., IEEE Electron Device Lett. **41**, 1185-1188 (2020).

[7] Q. Zhou, et al., 2011 International Electron Devices Meeting, pp. 33.4.1-33.4.4, Dec 2011.

[8] H. Lu, B. Hou, et al., IEEE Trans. on Electron Devices **68**, 3308-3313 (2021).

[9] S. Salahuddin, and S. Datta, Nano Lett. 8, 405-410 (2008).

#### **ACRONYMS**

HEMT: High Electron Mobility Transistor

SS: Subthreshold Swing

MOCVD: Metal-Oide Chemical Vapor Deposition

2DEG: Two-dimensional-electron-gas

PECVD: Plasma Enhanced Chemical Vapor Deposition

NDR: Negative Differential Resistance NCFET: Negative Capacitance Field Effect Transistor