# Micro Transfer Printing for Micro Assembly of Heterogeneous Integrated Compound Semiconductor Components

David Gomez<sup>1</sup>, James Thostenson<sup>1</sup>, Tanya Moore<sup>1</sup>, Kevin Oswalt<sup>1</sup>, Chris Reyes<sup>1</sup>, Ron Cok<sup>1</sup>, Alin Fecioru<sup>2</sup>

- 1. X-Celeprint Inc., 3021 Cornwallis Road, Research Triangle Park, NC 27709, USA

- 2. X-Celeprint Ltd., Tyndall National Institute, Lee Maltings Complex Dyke Parade, Cork, Cork, T12 R5CP, Ireland

## Keywords: Heterogeneous Integration, Micro-Transfer Printing, Micro Assembly

#### **Abstract**

Micro-Transfer Printing (MTP) is a mass transfer process that provides fast and precise assembly of microcomponents of a wide variety of shapes, sizes, and materials onto non-native substrates in a highly heterogeneously integrated fashion. The process involves fabricating retrievable micro-components, elastomer stamp retrieval, transfer-printing of the microcomponents to a non-native substrate, and finally electrical interconnection. Technology scaling requires an appropriate ecosystem realized by multiple suppliers and customers. The ecosystem includes source component supply, an industrial micro-transfer printer capable of handling wafers up to 300 mm, and commercial foundry capabilities. With these elements in place, MTP is now at a commercial stage that can support multiple customers and industries.

#### INTRODUCTION

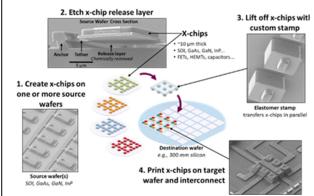

Micro-transfer printing (MTP) uses a rate-dependent micro-structured "print head" to transfer micro-scale devices that are MTP-compatible ("x-chips") from their native source substrates onto non-native target substrates. The process of MTP is summarized in Figure 1 and is briefly reviewed.

First, individual devices are fabricated in a dense array on traditional wafers, referred to as source material. (Figure 1, step 1). Source material can be manufactured at most semiconductor foundries with MEMS processing expertise. The lateral dimensions of the x-chips can range from a few micrometers to a few millimeters. The thickness of these x-chips can be as little as 1  $\mu$ m (and potentially thinner) and at least as thick as ~20  $\mu$ m, enabling MTP to safely handle small, brittle x-chips that are impossible to handle using conventional pick-and-place technologies. Then, using MEMS etch technology, an implanted release layer is chemically etched to singulate the x-chips from the source wafer substrate, leaving the x-chips suspended over the wafer by one or more anchor/tether structures (Figure 1, step 2).

Next, a large array of x-chips are picked up in parallel from the source wafer by a low-cost, reusable, viscoelastic stamp, breaking them free from the tethers. The stamp is micropatterned with small posts that adhere to the x-chips via

Figure 1: Overview of the MTP process used in an industrial setting.

van der Waals interactions (Figure 1, step 3). The custom post layout on the stamp matches the desired location of each x-chip on the source wafer, defined entirely by device designers. An MTP print tool controls the stamp motion. The picked-up x-chips on the stamp are then transferred, all in parallel, to a target wafer, with the location of each x-chip on the target wafer defined by the stamp with alignment accuracy of <1.0 μm at 3σ (Figure 1, step 4). This process can then be repeated, transferring x-chips from different source material to neighboring locations within the same receiving circuit with little to no change in placement accuracy[1]–[3].

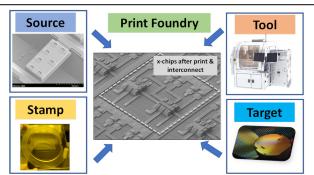

While MTP is a straight-forward process and has matured to an established mass-transfer technology over the last 15 years[4], [5], scaling the process to industrial high-volume levels requires an appropriate commercial manufacturing infrastructure, or ecosystem, supported by multiple suppliers and customers. Recently, such an ecosystem has been realized. The main components of this ecosystem correspond to the main process steps detailed above and in Figure 2. The components, shown in Figure 2 are: i) source material; ii)

MTP tool; iii) stamp; and iv) target material; all of which are leveraged within a Micro Transfer Print Foundry.

A recent effort has developed an industrial micro-transfer printer capable of handling wafers up to 300 mm (Figure 2), such as the ASM Amicra Nano and XDC transfer tools[6]. With these in place, MTP is now moving towards a commercial process that can support all parties seeking solutions to current heterogeneous integration issues.

## **EXPERIMENTAL**

#### Source Material

Wafers of various sizes are used to construct specific devices or materials for MTP processing. In order to fabricate x-chips, a sacrificial (release) layer and tether system is necessary. Many different release layers have been developed. Silicon with a <100> or <111> crystal plane orientation material is a common choice that is readily etched with TMAH or KOH. Many material systems can use this system, including some III-V materials that can be grown directly on silicon wafers or SOI substrates, where the oxide in the SOI stack allows for a barrier to the etch of the bulk silicon below the device. Several specific lattice-matched materials are listed in Table 1.

| Release Layer                    | Release Agent                                                                                                 | Substrate                     |

|----------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------|

| Buried Oxide (BOX) of<br>SOI     | HF (conc.)                                                                                                    | Silicon on Insulator<br>(SOI) |

| AlGaAs                           | HF or HCl                                                                                                     | GaAs                          |

| Si (111)                         | KOH or TMAH (hot)                                                                                             | Si (111)                      |

| InAlP                            | HCl                                                                                                           | GaAs                          |

| InGa(Al)As                       | FeCl <sub>3</sub> , H <sub>3</sub> PO <sub>4</sub> :H <sub>2</sub> O <sub>2</sub> or<br>citric acid: peroxide | InP                           |

| InP                              | HCl                                                                                                           | InP (InGaAs)                  |

| Si (100)                         | KOH or TMAH (hot)                                                                                             | Silicon on Insulator<br>(SOI) |

| LOR/PMGI                         | Developer                                                                                                     | Any                           |

| Parylene/PI                      | ${\rm O}_2$ plasma                                                                                            | Any                           |

| Ge                               | $\mathrm{H_2O_2}$                                                                                             | Any                           |

| T 11 1 T' 4 C 1 1 1 ' 4 ' 4'' 14 |                                                                                                               |                               |

Table 1: List of common release chemistries utilized to allow MTP source material to be produced.

Additional epitaxial layers can be deposited on specific release layers and fully formed components can be densely constructed on their native substrates. This decouples material growth on a native substate from material incorporation onto a higher (or lower) performance substrate material.

Figure 2: Ecosystem components required to create a MTP device.

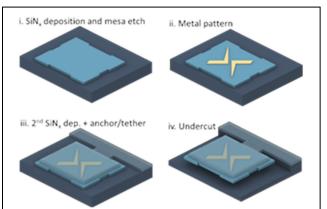

For the specific materials generated for the test results shown, a Si <100> wafer served as the release material. Figure 3 shows the fabrication flow for making the  $\mu$ TP-compatible 40  $\mu$ m x 40  $\mu$ m silicon nitride chips. In this case, the first and second silicon nitride layers' thickness are 0.6  $\mu$ m and 1.5  $\mu$ m, respectively. The released chips are each attached to the substrate with a silicon nitride tether attached to an anchor region that is not sacrificed during the anisotropic silicon release etching. In this system, the chips are at 50  $\mu$ m and 60  $\mu$ m pitch in the X and Y directions respectively.

Figure 3: Schematic representation of  $\mu TP$ -compatible 40  $\mu m \times 40~\mu m$  silicon nitride chips fabrication. (i) silicon nitride is deposited and patterned to form a mesa, (ii) thin-film metal is deposited and patterned to serve as an alignment feature, (iii) a second layer of silicon nitride is deposited and patterned to form the anchor/tether system, and (iv) the chip is released by anisotropic etching of the underlying silicon.

## Print Tool

ASM AMICRA has combined fundamental sub-micron motion-control knowledge with Dynamic Alignment technology to achieve 0.3 µm 3-sigma alignment for Si photonic devices transferred from source material to target substrate using MTP.[6] ASM AMICRA Dynamic Alignment views, aligns, measures, and confirms the source device placement accuracy to a target bond location in real time.

Dynamic Alignment provides three levels of bond measurement data that are saved for every attachment. Level 1 takes pre-placement measurements as the source material hovers very close to the substrate surface confirming location accuracy just prior to placing. Level 2 measurements are taken after placement but before the bond tool is removed from the source material. This confirms placement is as expected and within the placement accuracy required. Level 3 measurements are made after attachment release to calculate final placement data. This process eliminates "blind bonding" - the inability to view, align and measure real-time motion and placement during the bonding process. Blind bonding can introduce motion inaccuracies that diminish post-attach accuracy and inhibits a clear and documented optimization and understanding of placement that can fall outside the required target accuracies.

Fig. 4. ASM Amicra Nano MTP Tool.

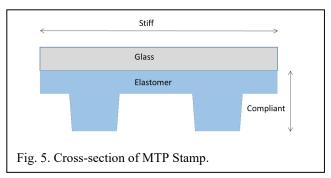

Stamp

Key attributes of MTP are inherent in an elastomeric printing stamp. The stamp consists of a rigid glass plate coated with an elastomeric layer with thousands of posts, one for each device to be transferred. A stamp cross-section is depicted in Fig. 5. A rigid glass plate as used as the base of the stamp. A subsequent layer of PDMS is cast against a silicon master. The stiff nature of the glass plate provides precise lateral control of the posts, enabling precision placement. The compliant nature of the PDMS in the Z

dimension enables PDMS compression. Post compression enables MTP from wafers to target substrates that are not flat as well as the ability to print into trenches.

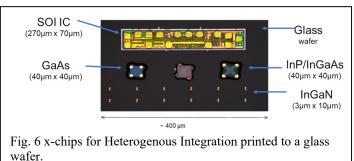

Target

The target material used for placement accuracy measurement was manufactured according to details provided in Gomez et al.[7] Target wafers are nominally coated with a thin resin to enable printing as well as with alignment marks for print material location identification and precise overlay measurements, although direct printing can take place if there is a sufficiently low roughness on the target and at the bottom of the source x-chip being transferred. Printed target materials include Silicon CMOS, glass, plastic, and ceramics. Figure 6 shows an example of multiple materials of multiple types and various sizes transferred to a single, common glass substrate.

## **RESULTS**

The Amicra Nano MTP tool process capability was tested. In this study, an array of 2x2 test chips were picked and printed into a  $500\mu m$  x  $700\mu m$  area and an array of 20x28 chips were picked and then printed into a 7mmx7mm area. Placement and yield measurements were taken on both arrays.

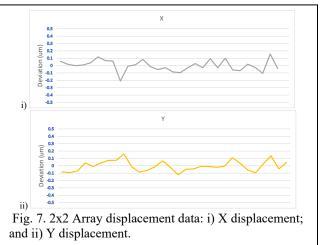

The 2x2 array of test chips provides 30 sets of measurements with 4 printed chips in each measurement, for a total of 120 transferred devices. Test chip placement in the X and Y dimension are shown in Figure 7 with a 3 sigma

value of 0.23 µm in the X and 0.21 µm in the Y direction. Each individual print has substantially the same precision, demonstrating excellent repeatability and a strong capability for MTP on the Amicra tool.

The previous results are for a relatively small array, so further work was completed with a 20x28 array measuring 7mm x 7mm in total area. These prints were done without tool intervention and each print of 560 x-chips was completed in 45 seconds. A larger stamp can print more devices, but care must be taken to optimize source wafer usage versus the cost in time to print the devices to the target wafers. These calculations are similar to the calculations that are commonly made with lithographic stepper field size. A 6-inch to 6-inch transfer of material from one wafer to another was completed, although such large transfers are best utilized when the wafer size of the source and target are matched.

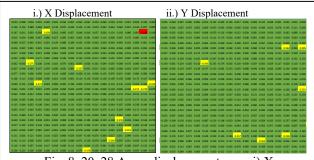

Figure 8 shows a single print map color coded with X and Y displacement values to illustrate any systematic issues that may be present. Values that are within +/- 0.25  $\mu m$  are highlighted in green; values that are within +/- 0.25 to +/- 0.5  $\mu m$  are highlighted in yellow. Values above 0.5  $\mu m$  and below -0.5  $\mu m$  are highlighted in red. Clearly, a large majority of the values are within the 0.25  $\mu m$  value.

Fig. 8. 20x28 Array displacement map: i) X displacement; and ii) Y displacement.

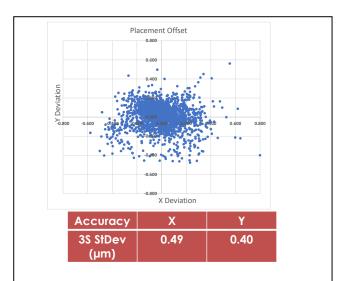

Figure 9 graphically illustrates the device print displacement. In this graph, the four prints showed a 3 sigma value of  $0.49\mu m$  for the X displacement and  $0.40\mu m$  for the Y displacement. Such high printing precision is particularly useful for photonic applications requiring careful component alignment.

This data demonstrates that the Amicra Nano Tool is a capable and valuable tool in an industrial micro-transfer printing ecosystem. Such commercial tools enable customer at-scale material processing in any manufacturing setting. We look forward to further increasing performance and expanding the ecosystem for heterogenous integration using the MTP platform.

### CONCLUSIONS

The increasing interest in micro-transfer printing (MTP) has established an ecosystem of services, tools, and foundries has been established. An industrial-scale MTP tool is the most recently established component in this ecosystem. The MTP

Fig. 9 . 20x28 Array displacement map data for all four prints within 3 sigma for entire dataset.

ecosystem enables small and often fabless companies to incorporate MTP into their processing to lower cost, simply integrate diverse micro-devices, and assemble devices much smaller than possible with pick-and-place tools or at layout-spacings not achievable with die-bonding. This ecosystem is currently available and shows promise in meeting the needs of the photonics and defense industrial base.

## ACKNOWLEDGEMENTS

The authors would like to thank Amicra, Micross, X Display, and X-Celeprint for their contributions.

### REFERENCES

- [1] D. Gomez *et al.*, "Scalability and Yield in Elastomer Stamp Micro-Transfer-Printing," no. c, pp. 1779–1785, 2017.

- [2] M. Meitl *et al.*, "55-1: Invited Paper: Passive Matrix Displays with Transfer-Printed Microscale Inorganic LEDs," *SID Symp. Dig. Tech. Pap.*, vol. 47, no. 1, pp. 743–746, 2016.

- [3] C. A. Bower, M. A. Meitl, S. Bonafede, D. Gomez, A. Fecioru, and D. Kneeburg, "Heterogeneous integration of microscale compound semiconductor devices by micro-transfer-printing," *Proc. Electron. Components Technol. Conf.*, vol. 2015-July, pp. 963–967, 2015.

- [4] P. Garou, "IFTLE 484: Massively Parallel Pick-and-Place Assembly from the X-Men," 3DInCites, 2021. [Online]. Available: https://www.3dincites.com/2021/05/iftle-484-massively-parallel-pick-and-place-assembly-from-the-x-men/.

- [5] J. O. Thostenson and J. Roe, "Micro-transfer printing From wafer to wherever," *PIC Magazine*,

- no. 4, 2019.

- [6] J. Weinhaendler, B. Conner, L. Ee Guan, and C. Burke, "ASM AMICRA Unveils Industry's First Manufacturing Systems Incorporating X-Celeprint's MTP Technology for High Volume Heterogeneous Integration of Ultra-Thin Chips," ASM Amicra, 2021. [Online]. Available: https://amicra.com/news/news/item/165-asm-amicra-unveils-industry-s-first-manufacturing-systems-incorporating-x-celeprint-s-mtp-technology-for-high-volume-heterogeneous-integration-of-ultra-thin-chips.

- [7] D. Gomez *et al.*, "Process Capability and Elastomer Stamp Lifetime in Micro Transfer Printing," in *2016 IEEE 66th Electronic Components and Technology Conference (ECTC)*, 2016, vol. 2016-Augus, pp. 680–687.