# Reliability Assessment of 940 nm VCSEL Array based on Pulsed Mode Thermal Analysis

Fan-Hsiu Huang, Yin-Hsiang Lin, Chun-Tse Chang, Kai-Lun Chi and Ming-Wei Tsai

WIN Semiconductors Corp. Guishan District, TaoYuan City, 333, Taiwan E-mail: yhlin@winfoundry.com, fhhuang@winfoundry.com

# Keywords: VCSEL, pulsed mode, thermal analysis

#### Abstract

In order to obtain a relative accuracy of lifetime prediction of reliability test for VCSEL array device, the junction temperature  $(T_j)$  extraction has been investigated and analyzed in this manuscript. We propose a modified array thermal model which is achieved by unit area including  $2 \times 2$  emitters based on the thermal characterizations of single emitter and array device. Adopting the additional parameters of thermal coupling and common thermal dissipation path into the model, peak and average  $T_j$  can be analyzed for the VCSEL array within 380 emitters under pulsed or CW operation.

To further verify the  $T_j$  extraction with a certain pulse condition, accelerated life testing (ALT) was performed for a criteria of 5 % power degradation at operating current  $(I_{op})$ . The array lifetime prediction can be analyzed by the calculation of temperature acceleration factor  $(E_A)$  and current acceleration factor (n) with the modified  $T_j$  value.

# Introduction

In order to meet the requirements for data communication, current density of a single VCSEL is much higher than a typical emitter in a VCSEL array device for high power applications. Typically, reliability estimation/analysis of a datacom VCSEL is based on CW current stress [1-2]. With VCSEL array for high power applications such as 3D sensing and Time of Flight, there are the added concerns for eye safety requirements. Therefore these, array-type VCSEL devices are operated under pulse Achieving optimal electrical-to-optical [3-4]. conversion efficiency for each VCSEL emitter becomes critical especially for larger array VCSEL devices to minimize high power consumption and meet reliability requirements. In this work, we present a lifetime reliability analysis by the proposed thermal model for pulsed mode operation with a specific pulse width and duty cycle. It would be a modification to examine acceleration factor (AF) parameters to approach an improvement of lifetime prediction for accelerated life test (ALT) or high temperature operating life (HTOL) tests.

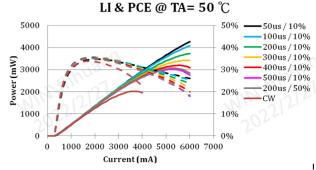

Figure. 1. Output power versus current at 50 °C for CW mode and pulsed mode with different pulse width.

### VCSEL DESIGN

The tested chips are front side emitter VCSEL array with oxide-confined aperture. The ion-implantation makes isolation on the surface. The epitaxy is grown on an n-type GaAs substrate with three multi-quantum wells sandwiched between n-type and p-type distributed Bragg reflector (DBR) layers with an Al<sub>0.98</sub>Ga<sub>0.02</sub>As layer above the MQWs for oxidation. In order to expose the oxide layer, the etching pattern is trench-type and is made by an inductive coupled plasma (ICP) reactive ion etching. The etch depth is controlled by in situ reflectivity measurement system. The oxide aperture is formed by the selective wet oxidation converting Al<sub>0.98</sub>Ga<sub>0.02</sub>As to Al<sub>x</sub>O<sub>y</sub> at a specific temperature. The test VCSEL array device contains 380 emitter elements with emitter pitch of 31  $\mu$ m, and chip size of  $848 \times 746 \ \mu\text{m}^2$ . Oxide aperture diameter of each emitter is about 10 µm. The test device was packaged via die attach to copper-plated TO can package for thermal management. The test device was evaluated for thermal and reliability characteristics.

Figure 1 shows light-current (L-I) curves and corresponding power conversion efficiency (PCE) from 50 to 500  $\mu$ s pulse duration @ 10% duty cycle, 200  $\mu$ s pulse @ 50% duty cycle and CW test conditions. The maximum PCE is close to 35 % at an optical output power of 1.3 W. Peak optical power reduces at longer pulse condition as expected due to thermal effect. Since reliability depends on the junction temperature, a proper pulse-mode output power is typically half of the peak power close to maximum PCE.

The operating output power of the test VCSEL array is around 2 W at the operating current ( $I_{op}$ ) of 3 A (11  $kA/cm^2$ ).

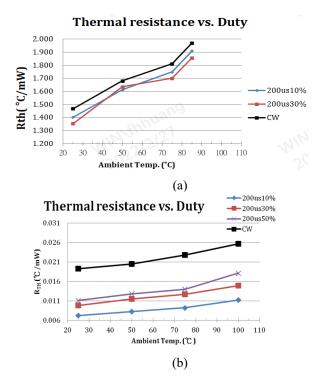

Figure 2. Thermal resistances versus duty cycles at threshold current level (pulse width= $200 \mu s$ ): (a) single emitter (duty cycle: 10 %, 20 %, and CW), (b) array device (duty cycle: 10 %, 20 %, 50% and CW).

## JUNCTION TEMPERATURE EXTRACTION METHOD

According to the proposed method [5], emission spectra detection is general method to measure junction temperature  $(T_j)$  for single emitter VCSEL device, which is using wavelength shift to calculate  $T_j$  with wavelength temperature coefficient  $(R_{\lambda})$  and the dissipated power as a function of wavelength:

$$T_{\rm j} = T_{\rm A} + (\lambda_1 - \lambda_0) R_{\lambda} \tag{1}$$

where  $R_{\lambda}$  is wavelength temperature coefficient (nm/°C).

However, the effects of thermal coupling and mode hopping usually occur in VCSEL array devices with large number of single emitters, which would lead to temperature detection error and an underestimation of  $T_j$  characteristic. For a high-power semiconductor laser, the modified  $T_j$  measurement has been proposed with regard to electrical-to-optical conversion efficiency [6].

$$T_{\rm i} = T_{\rm A} + R_{\rm TH} \times (I \times V - P_{\rm O}) \tag{2}$$

$$R_{\rm TH} = \frac{\Delta^{\circ}C}{\Delta W} = \frac{\Delta^{\circ}C/\Delta\lambda}{\Delta W/\Delta\lambda} = \frac{1}{R_{\lambda} \times R_{\rm diss}}$$

(3)

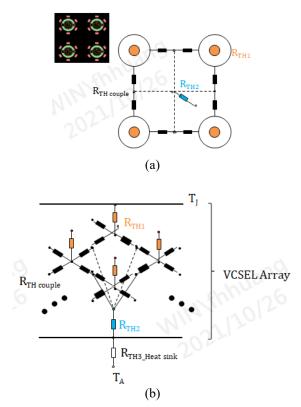

Figure 3. Thermal model of VCSEL array: (a) unit area ( $2\times2$  emitters) within thermal coupled  $R_{TH,couple}$  and  $R_{TH2}$ , (b) the completed array schematic (380 emitters) with  $R_{TH3,heat\,sink}$ .

where  $P_{\rm o}$  is optical power under operation current,  $R_{\lambda}$  is wavelength temperature coefficient, and  $R_{\rm diss}$  is dissipated power as a function of wavelength. To measure  $R_{\rm diss}$ , the peak wavelength must be recorded at the fundamental mode when the current is slightly above threshold current level.

Based on a typical method,  $R_{\rm TH}$  were extracted for single emitter and array devices under pulsed operation with different duty cycles were analyzed as shown in Figure 2. The data shows that  $R_{\rm TH}$  value is not a constant, but is dependent on  $T_A$ . At higher  $T_A$  operating condition a VCSEL quantum efficiency and optical power generally decrease this is equivalent to an increase in  $R_{TH}$ . Figure 2 (a) shows an almost  $\Delta R_{\rm TH}$  of 0.5 °C/mW in single emitter while setting  $T_{\rm A}$ up to 85 °C. For an array device, T<sub>i</sub> characteristic is also impacted by the emitter pitch and thermal dissipation capability from the heat sink. Figure 2 (b) demonstrates  $R_{\text{TH}}$ of the array device with the maximum  $T_A$  of 100 °C. The data shows that the overall  $R_{TH}$  value of the array VCSEL is lower than that of a single emitter. The measurement results imply that the peak  $T_j(T_{j,peak})$  values are different for a single emitter and an array device when  $T_j$  is derived directly from  $R_{\rm TH}$ . Theoretically,  $T_{\rm i,peak}$  should be the same value for a pulsed mode operation, when a single emitter and an array devices are driven at the same current density. This means that T<sub>i</sub> derived by this method for each VCSEL emitter in the array device at Iop or higher applied current underestimates

the actual junction temperature in comparison to a single VCSEL at the same current density.

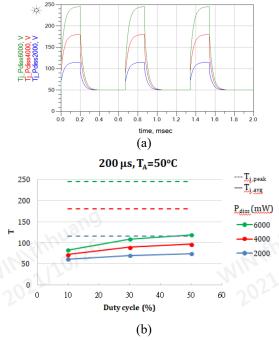

Figure 4. Simulation of thermal behavior ( $T_A=50^{\circ}$ C, pulse width=200 µs): (a) transient waveform with power dissipations of 2.0, 4.0, and 6.0 W (duty cycle=20 %), (b)  $T_{\rm i,avg}$  and  $T_{\rm i,peak}$  with different duty cycles.

Furthermore, we can only detect average  $T_j(T_{j,avg})$  at lower duty cycle due to the limitation of thermal measurement within the sampling detection limit [7]. In practical, the  $T_{j,avg}$ is lower than  $T_{j,peak}$ . This makes difficult to perform an accurate lifetime analysis through the typical reliability test. To achieve improved estimate of  $T_i$  for reliability analysis, a modified thermal model for a VCSEL array is shown in Figure 3. Figure 3 (a) shows a unit area including  $2 \times 2$ emitters. For a small pitch distance between emitters, 2 thermal resistances,  $R_{\text{TH,couple}}$  and  $R_{\text{TH2}}$ , are adopted to describe thermal coupling effect and a common thermal path. Figure 3 (b) displays the completed model with heat sink ( $R_{\text{TH,heat sink}}$ ). Based on the thermal model, we can analyze transient thermal behavior with any power dissipations ( $P_{\text{diss}}$ ) and duty cycles by simulation. Setting  $P_{\rm diss}$  at 2.0 W, 4.0 W, and 6.0 W, calculated  $T_{\rm j,peak}$  and  $T_{\rm j,avg}$ are shown in Figure 4 (a). To further make a precise  $T_i$ simulation, we calibrated the thermal parameters in the model by the measured  $T_{j,avg}$  at various duty cycles. Figure 4 (b) shows the result of  $T_{j,peak}$  and  $T_{j,avg}$  versus duty cycles after the calibration. This means that we can determine the reasonable test conditions of duty-cycle dependence and current density for lifetime reliability test and analysis.

## VCSEL RELIABILITY TEST

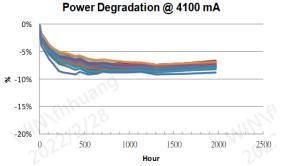

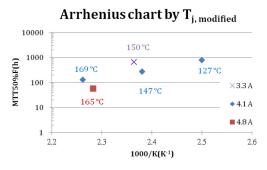

The most common accelerated aging is achieved by controlling current and junction temperature. The challenge is how to accurately measure junction temperature under pulsed mode operation, which can affect  $E_A$  extraction and lifetime prediction [4]. In order to understand the reliable operating conditions for the VCSEL array, MTTF test has been performed relying on  $T_{j,modified}$  values which is a new factor calculated from  $T_{j,avg}$  and  $T_{j,peak}$ . The test condition list for the test is presented in TABLE I, where the pulse width is 200 µs with duty cycle of 30 %. Figure 5 shows the plot of optical power degradation versus time with the test condition of I=4100 mA and  $T_{i,modified}=169$  °C. The result exhibits a stable degradation of 8 % after 500 hours of stress without reaching the typical failure criteria, 10 % degradation. For the lifetime analysis, we set 5 % power degradation at  $I_{op}$  to be the failure criteria. Figure 6 plots the Arrhenius life-stress acceleration within 3 current densities and 3 modified temperatures, where the current densities were set at 11, 13.7, and 16.1  $kA/cm^2$ , respectively.

TABLE I CURRENT DENSITIES AND  $T_{j,modified}$  CONDITIONS FOR DC STRESS

| I(A) | $J_{D} (kA/cm^{2})$ | T <sub>A</sub> =55 °C | T <sub>A</sub> =70 °C | T <sub>A</sub> = 83 °C |

|------|---------------------|-----------------------|-----------------------|------------------------|

| 3.3  | 11.1                |                       |                       | 150 °C                 |

| 4.1  | 13.7                | 127 °C                | 147 °C                | 169 ℃                  |

| 4.8  | 16.1                |                       | 165 °C                |                        |

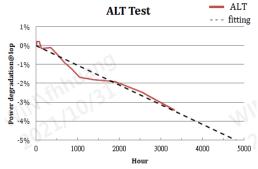

The unreliability for time to failure was set to be 50 %. After the time-to-failure analysis, we obtain the calculated AF values of temperature acceleration factor  $E_A$ =0.68 eV and current acceleration factor n=4.7 as shown in Table II. The experiment shows a high n value compared to the published reports [3]. This means that another electrical characteristic also impacts the reliability result besides the pulsed  $T_{i,modified}$  extraction. The cause of the phenomena is the so-called lateral sheet resistance degradation which has been investigated in [8]. Due to the mechanism of a defect being generated in the oxidation and diffusing into the surrounding P-type mirror layers and diffusion/drift of the unpaired interstitial hydrogen donors into the surrounding isolation implant region, lateral junction causes an increase of threshold current. To remove the acceptor compensation effect, a process of high-temperature anneal has to be performed after oxidation process. Although the current acceleration factor is beyond the typical value, we tried to verify the lifetime prediction based on the MTTF test result. ALT was performed to check degradation trend with 96 samples. Figure 7 shows the trend of power degradation in the test. The samples were stressed tested at 11.7 kA/cm<sup>2</sup> with 10 % duty cycle, and  $T_{i,modified}$  was set at 147 °C with T<sub>A</sub>=85 °C. The optical output power was tested at I<sub>op</sub> every

24 hours. The result depicts a reasonable estimate time around 4,500 hours to achieve 5 % power degradation.

Figure 5. Optical power degradation plot at I=4100 mA and  $T_{j,modified}$ =169 °C.

Figure 6. Arrhenius plot for a criteria of 5 % power degradation at operating current ( $I_{op}$ ), where the current were set at 3.3, 4.1, and 4.8 A, respectively.

TABLE II ACTIVATION ENERGY  $(E_A)$  AND CURRENT ACCELERATION FACTOR (n) OF THE VCSEL ARRAY

| Factor      | This experiment |  |

|-------------|-----------------|--|

| $E_{\rm A}$ | 0.68            |  |

| n           | 4.7             |  |

Figure 7. Power degradation trend chart in ALT test at operating current ( $I_{op}$ ), and  $T_{j,modified}$  was set at 147 °C.

#### **CONCLUSIONS**

This work demonstrates a lifetime reliability analysis for VCSEL array under pulsed mode operation. By contrast to the conventional  $T_j$  measurement, thermal coupling effects among emitters in the array and peak junction temperature analysis have been investigated. Through building up a thermal model with  $R_{TH,couple}$ , 2 temperatures,  $T_{j,avg}$  and  $T_{j,peak}$ , can be easily obtained by the simulation of transient behavior with different power dissipations and duty cycles.

By the MTTF test result with the dedicated pulse width and the extraction of acceleration parameters, a non-typical n value presents in this experiment. To further modify the current acceleration factor, process modification and development of burn-in condition have to be taken into account for improving the device characteristic under high current operation. Based on this methodology for pulsed-mode thermal analysis, we now have a model to accurately predict the lifetime of array VCSEL devices under a specific pulse width and duty cycle.

#### REFERENCES

- [1] Ian Aeby et al., "Highly reliable oxide VCSELs for datacom applications", *Proceedings of SPIE*, vol. 4994, 2003.

- [2] A. Mereuta et al., "10-Gb/s and 10-km error-free transmission up to 100°C with 1.3-µm wavelength waferfused VCSELs", *Optics Express*, vol.17, no.15, Jul., 2009.

- [3] Luke A. Graham et al., "High power VCSEL arrays for consumer electronics", *Proc. of SPIE*, vol. 9381, 2015.

- [4] B. Petrov et al., "Broad range pulse widths reliability model for 905 nm high power lasers", *Proceedings of SPIE*, vol. 11668, 2021.

- [5] M. Xun et al., "Analysis of thermal properties of 940-nm vertical cavity surface emitting laser arrays", *IEEE Trans. on Electron Devices*, vol.68, no.1, Jan., 2021.

- [6] "VCSEL Thermal Performance", Vixar Application Note, 2019.

- [7] V. G. Garcia, "Transient thermal imaging of a vertical cavity surface-emitting laser using thermoreflectance microscopy", *Journal of Applied Physics*, vol.119, Jan., 2016.

- [8] B. M. Hawkins et al., "Reliability of Various Size Oxide Aperture VCSELs", 52<sup>nd</sup> Electronic Components and Technology Conference 2002, Aug., 2002.