# How to Unleash Power of Ga<sub>2</sub>O<sub>3</sub>?

Huili Grace Xing<sup>1,2,3</sup> Wenshen Li<sup>1</sup>, Zongyang Hu<sup>1</sup>, Kazuki Nomoto<sup>1</sup>, Devansh Saraswat<sup>2</sup>, Bennett Cromer<sup>2</sup>, Kathleen Smith<sup>4</sup>, Emma Long<sup>2</sup>, Mingli Gong<sup>2</sup>, and Debdeep Jena<sup>1,2,3</sup>

<sup>1</sup>School of ECE, <sup>2</sup>Department of MSE, <sup>3</sup>Kavli Institute for Nanoscience, <sup>4</sup>Department of AEP

Cornell University, Ithaca, NY 14853 USA

grace.xing@cornell.edu, (phone) 607-255-0605

Keywords: Ga<sub>2</sub>O<sub>3</sub>, power electronics, UWBG, Schottky Barrier, p-n junction, transistor

In this invited talk I will discuss how and why my research group started to study Ga<sub>2</sub>O<sub>3</sub>, what questions we set out to answer and what we have learned. These learnings prompted us to develop some guiding principles in designing power electronics employing ultra-wide bandgap semiconductors (UWGBs).

#### INTRODUCTION

[Adapted from Ref. 1] It's of little surprise that there has been a consistent drive toward the use of wider bandgap materials for power electronics. After all, the wider the bandgap, the greater the breakdown field, opening the door to making devices with a higher breakdown voltage for the same material thickness.

However, nature is not always that generous. Typically, a move to a wider bandgap is accompanied by more challenging doping, along with difficulty in making high-quality native substrates. Judged in these terms, gallium oxide appears to offer a sweet spot beyond SiC and GaN.

One of the most promising forms of gallium oxide is its β-phase, which has a bandgap of 4.5-4.7 eV. Luckily, it is easy to dope this oxide n-type in a controllable manner, to realize doping that spans 10<sup>15</sup> cm<sup>-3</sup> to 10<sup>20</sup> cm<sup>-3</sup>. Thanks to shallow donor levels throughout this range, doping efficiency is high at room temperature. Another encouraging aspect of Ga<sub>2</sub>O<sub>3</sub> is that single-crystal substrates of this material can be readily produced with melt-growth techniques, mirroring the manufacture of those made from silicon. On the other hand, the thermal conductivity Ga<sub>2</sub>O<sub>3</sub> of is rather low, and it is most likely impossible to dope Ga<sub>2</sub>O<sub>3</sub> p-type. Given all these promises and obstacles, is it possible to harvest all the benefits arising from the large bandgap of Ga<sub>2</sub>O<sub>3</sub> and demonstrate devices that are superior to those made from SiC and GaN?

# HOW WE STARTED

The first time I heard of single crystalline  $Ga_2O_3$  was about the early demonstrations of vertical GaN LEDs on  $Ga_2O_3$  demonstrated by Kuramata et al. [2] and Shimamura et al. [3] in 2005. It is exciting to find another transparent conducting oxide, this time, with a bandgap higher than of ITO (4.5-4.7 eV versus 4 eV for ITO). Around 2010, Masataka

Highashiwaki, who recently left UCSB to join NICT in Japan, visited our research group and he excitedly shared the new research direction he decided to pursue: Ga<sub>2</sub>O<sub>3</sub> electronics. During that time, I was deeply involved in highly-scaled GaN transistors aiming to answer whether it is feasible to achieve THz operation in GaN, and the underlying physical phenomena. The other two projects I was deeply engaged in were tunnel FETs and 2D materials – both were exciting new fields and much of their physics and properties awaited for discovery.

My close collaborator, Prof. Debdeep Jena (DJ), remained interested enough to secure a Ga<sub>2</sub>O<sub>3</sub> crystal cube about 1 cm<sup>3</sup> from Zbigniew Galazka at IKZ, Berlin in 2012. I still recall the day we were enjoying a Friday happy hour with Dr. Galazka at the Legends at the University of Notre Dame, discussing bulk crystal growth in general and in particular, Ga<sub>2</sub>O<sub>3</sub>. One day, Dr. Wan Sik Hwang, then a postdoc working with DJ, reported with excitement: I exfoliated flakes of Ga<sub>2</sub>O<sub>3</sub> using Scotch tape! DJ replied: Let us make a field effect transistor (FET) out of it, just like the other 2D materials we have been studying! We will know the carrier mobility and the max field it can stand. This led to the first publication on the high-voltage FET with wide-bandgap Ga<sub>2</sub>O<sub>3</sub> nanomembrane [4]. Subsequently, DJ also led the investigation of thermal conductivity of Ga<sub>2</sub>O<sub>3</sub> and the fundamental limits of electron mobility in Ga<sub>2</sub>O<sub>3</sub>. This part of the history has been narrated by him in his book chapter in Gallium Oxide: Crystal Growth, Material Properties and Devices, Springer, edited by Masataka in 2020.

## WHICH SEMICONDUCTOR FOR POWER

I decided to compare power electronic device performance between Ga<sub>2</sub>O<sub>3</sub> and GaN after I started to lead an ARPAe SWITCHES project on GaN-on-GaN vertical power transistors in 2013 then subsequently moved to Cornell in 2015 (therefore a setback on pursuing Ga<sub>2</sub>O<sub>3</sub>). After nearly 3 decades of GaN growth and device technology advancement, at that time it was not yet clear whether GaN is able to avalanche, and if so, under what circumstances. There were a few reports in the literature claiming observations of signs of avalanche, however, it was difficult to prove due to lack of independent measurements. The world first report on convincing avalanche in GaN was reported by the Avogy (a

startup focusing on vertical GaN-on-GaN power electronics) in 2013 in a GaN p-n homojunction [5]. The second report is by my research group: Dr. Kazuki Nomoto fabricated high-quality GaN p-n diodes on wafers obtained from the Hitachi Cable (now SCIOCS); and he presented the results and analysis at IEDM 2015 [6]. Dr. Zongyang Hu in my group also reported in 2015 for the first time near unity ideality factor, simultaneously achieved with avalanche breakdown, and SRH carrier lifetime in GaN p-n junctions using epiwafer grown by IQE [7]. I still recall the excited and sometimes sharp questions from the IEDM audience, including "what are the advantages of such a vertical device compared to the lateral GaN HEMT or SBDs?", "what is the use to have a rectifier based on p-n junction that will unavoidably have a higher turn-on voltage than a Schottky barrier diode?"

I had some answers for these questions. One is that p-n junctions can readily afford avalanche breakdown, which subsequently enable one to probe the intrinsic properties of The other one is that p-n junction based edge termination technologies, for any power electronic device embodiment, are the best one can fully take advantage of what a material offers. Yes, a SBD typically has a lower turn-on voltage and often sufficient to be used in a power electronic circuit. However, if one does not desire to grossly underrate a SBD, it is the best to design a SBD that avalanches. That is why the best power SBD is actually JBSDs, where 3D p-n junctions are employed to manage the electric field crowding and provide surge capabilities. Both GaN and Ga<sub>2</sub>O<sub>3</sub> still face this challenge today – how to implement reliable 3D p-n junctions. For these reasons, we proposed and demonstrated trench JBSDs in GaN [8], and high-work function p-type oxide metal grown by MBE for Ga<sub>2</sub>O<sub>3</sub> SBDs [9].

From 2016 to 2020 my research group designed and fabricated several generations of Ga<sub>2</sub>O<sub>3</sub> vertical trench SBDs and FinFETs, establishing firsts and new record performances [10-18]. It is worth noting that the Palacios' group at MIT investigated vertical FinFETs for the first time in GaN with insulated gates in 2016 [19] while the previously studied vertical double-gated or gate-all-around FETs had been grouped under different names, including static induction transistor (SIT) - possessing a same device topology as vertical MESFETs, vertical JFETs, and explicitly vertical MESFETs. These devices were explored for the first time mostly in the GaAs materials system back in 1980s and 1990s, and later in SiC. Given MOS junctions were poorly understood in these material systems at that time, Schottky junctions and p-n junctions were employed. In addition to the gate structure difference, the primary difference between a SIT and a vertical FinFET is their operation region: a SIT typically operates in the linear triode region thus with a short gate length and a vertical FinFET typically operates in the saturation region of a transistor.

In addition, we reported for the first time the crystalline orientation dependent interfacial charge densities [20] and their impact on the on-resistance of trench SBDs [21]. With the research group at Padova, we examined trapping and de-

trapping mechanisms in Ga<sub>2</sub>O<sub>3</sub> FinFETs and compared with that in GaN FinFETs [22]. With S. Choi's group, we examined the thermal design considerations of multi-fin Ga<sub>2</sub>O<sub>3</sub> vertical transistors [23]. With M. Kuball's group, we studied the breakdown mechanisms in the trench SBDs [24].

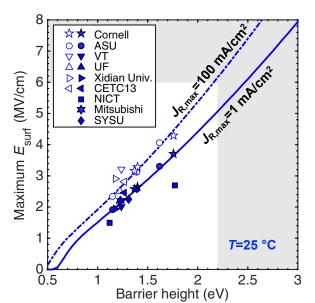

Fig. 1. Adopted from Ref. 22. Calculated reverse leakage current in a Ga<sub>2</sub>O<sub>3</sub> SBD versus what has been reported by various groups around the world. Excellent match is observed. This result confirms a barrier height >2.2 eV is necessary to reach a surface field as high as 6 MV/cm.

More importantly, we set out to answer a fundamental question: how to harvest the high electric field a (ultra)wide bandgap semiconductor offers? To this end, we re-visited the transport mechanisms in p-n junctions [5] and Schottky junctions [25]. We discovered a simple trend to describe the transition region between thermionic emission (TE) and thermionic field emission (TFE) transport in a SBD [26]. We proposed a unified TE-TFE analytical model and validated the model over a large range of semiconductors from Si ( $E_g =$ 1.1 eV, indirect) to  $Ga_2O_3$  (E<sub>g</sub> = 4.5 eV) [27], which highly simplifies calculations in a SBD by 10,000 times. It is particularly attractive to be employed in TCAD simulations since computation time and convergence are often encountered with the iterative numerical calculations currently adopted in the commercial TCAD tools. Combined with the guiding principles in how to design trench SBDs [28], the analytical model approves to be very handy.

Based on these systematic studies, we have made several recommendations on how to achieve an electric field as high as 6 MV/cm, which is likely close to but still smaller than what an intrinsic Ga<sub>2</sub>O<sub>3</sub> affords. To avoid plagiarize myself, Fig.1 illustrates one result showing the calculated and

reported reverse bias current in a SBD. More details can be found in the sections Wenshen Li and I wrote in the recent roadmap article on Ga<sub>2</sub>O<sub>3</sub> power electronics that Andy Green (AFRL), Jim Speck (UCSB) and I orchestrated [26].

#### **CONCLUSIONS**

WBGs and UWBGs are exciting materials to work with. As our community continues to improve the material quality as well as the quality of processing these materials, we will gradually reveal the intrinsic properties of them. Excellent device physics is found in excellent devices, which is particularly true for high-field transport related physical phenomena.

## **ACKNOWLEDGEMENTS**

The authors would like to thank all the other collaborators and co-authors studying Ga<sub>2</sub>O<sub>3</sub> and GaN power electronics, especially the students and the faculty at the Cornell ACCESS center. The authors are thankful for the support from ULTRA (analytical modeling), an Energy Frontier Research Center funded by the U.S. Department of Energy (DOE), Office of Science, Basic Energy Sciences (BES), under Award No. DE-SC0021230. The work is also supported, in part, by the Air Force Office of Scientific Research (AFOSR) (No. FA9550-20-1-0148, numerical modeling), ComSenTer (experimental validation), one of the six SRC JUMP centers, and ACCESS (Ga<sub>2</sub>O<sub>3</sub> SBDs), an AFOSR Center of Excellence (No. FA9550-18-1-0529). This work made use of the Cornell Center for Materials Research Shared Facilities that are supported through the NSF MRSEC program (Grant No. DMR-1719875). This work was performed, in part, at the Cornell NanoScale Facility, a member of the National Nanotechnology Coordinated Infrastructure (NNCI), which is supported by the National Science Foundation (Grant No. NNCI-2025233).

## REFERENCES

[1] W. Li, H. G. Xing *et al.* Compound Semiconductor, April/May Issue, Page 22-28 (2019).

https://compoundsemiconductor.net/article/106964/Unleashing The Promise Of Gallium Oxide

- [2] Kuramata, A. Ga<sub>2</sub>O<sub>3</sub> Crystal and its LED application. *Bull. Solid State Phys. Appl. (Jpn. Soc. Appl. Phys.)* **2013**, *19*, 42.

- [3] Shimamura, K.; Víllora, E.G.; Domen, K.; Yui, K.; Aoki, K.; Ichinose, N. Epitaxial Growth of GaN on (1 0 0) β-Ga<sub>2</sub>O<sub>3</sub> Substrates by Metalorganic Vapor Phase Epitaxy. *Jpn. J Appl. Phys.* **2005**, *44*, L7–L8.

- [4] Wan Sik Hwang *et al.*, High-Voltage Field-Effect Transistors with Wide-Bandgap Ga<sub>2</sub>O<sub>3</sub> Nanomembranes *Appl. Phys. lett.* 104 203111 (2014).

- [5] I. C. Kizilyalli *et al.*, IEEE Trans. Electron Devices 60, 3067 (2013)

- [6] K. Nomoto et al., IEEE IEDM 9.7 (2015)

- [7] Z. Hu et al., Appl. Phys. Lett. 107, 243501 (2015)

- [8] W. Li *et al.*, IEEE Trans. Electron Dev. 64(4), 1635-1641 (2017) on trench JBSD

- [9] D. Saraswat et al., DRC (2020)

- [10] Z. Hu et al., DRC (2017) on vertical Ga<sub>2</sub>O<sub>3</sub> FinFETs DOI: 10.1109/DRC.2017.7999512

- [11] W. Li, et al., DRC (2018) on trench SBDs

- [12] W. Li, et al., IEDM (2018) on trench SBDs

- [13] W. Li, et al., APL (2018) on ultra-low leakage SBDs

- [14] Z. Hu et al., ISPSD (2019) on field-plated FinFETs

- [15] W. Li., et al, DRC (2019) on barrier stability

- [16] W. Li, et al., DRC (2019) on 0.78 GW/cm<sup>2</sup> SBDs

- [17] W. Li, et al., IEDM (2019) on FinFETs

- [18] W. Li, et al., IEEE EDL (2020) on 0.95 GW/cm<sup>2</sup> SBDs

- [19] M. Sun, M. Pan, X. Gao, and T. Palacios, "Vertical GaN power FET on bulk GaN substrate," in 2016 74th Annual Device Research Conference (DRC), 2016, pp. 1–2. DOI: 10.1109/DRC.2016.7548467

- [20] W. Li, et al., APEX (2019) on fin orientation dependence

- [21] W. Li, et al., IEEE TED (2021) on Ron

- [22] E. Fabris et al., IEEE TED 67, 3954 (2020)

- [23] B. Chatterjee et al., APL 119 (2021)

- [24] T. Moule, et al., IEEE TED (2022)

- [25] W. Li, et al., APL 116, 192101 (2020) on near ideal SBDs

- [26] W. Li, et al., APL 117, 222104 (2020) on TE or tunneling?

- [27] W. Li et al., J. Appl. Phys. 131, 015702 (2022) on the unified TE-TFE model.

- [28] W. Li. et al., IEEE TED, 67, 3938 (2020) on guiding principles in designing trench SBDs.

- [26] A. J. Green, J. Speck, H. G. Xing et al. APL Mater. 10, 029201 (2022) Roadmap Collection.

# ACRONYMS

FET: Field Effect Transistor SBD: Schottky Barrier Diode

JBSD: Junction Barrier Schottky Diode